[개요]

1. 논리 회로

- Combinational Logic (조합 논리 회로)

: input이 주어지면, output이 고정된다.

output이 다음 output에 영향을 주지 못 함.

- Sequential Logic (순차 논리 회로)

: 이전 output이 다음 output에 영향을 줄 수 있다.(Feedback)

clock을 사용함.

2. Modeling 기법

동작 레벨(Behavioural Level)

동작적 모델링(Behavioural Modeling) : C언어와 가상 유사한 방법이며, 설계의 기능을 알고리즘 위주로 기술하는 방법. 하지만 Synthesis하 는 과정에서 LUT나 Flip Flop들이 지나치게 사용될 수 있다.

initial(Time = 0 일떄 실행되는 구문), always(내부 구문을 반복 실행하는 무한루프 같은 구문) 등의 구문을 주로 사용

데이터플로우 모델링(Dataflow Modeling) : 시스템 내에서 데이터가 어떻게 이동하는지 나타내며, 일반적으로 레지스터 사이의 데이터 이동 을 나타낸다.

assign (delay) (list_of_assignments)

딜레이는 옵션이며, list_of_assignments는 (c = a & b); 같은 형식으로 표현한다.

구조 레벨(Structural Level)

구조적 모델링(Structual Modeling) : 논리 게이트를 사용하는 가장 낮은 레벨의 모델링 방법. Gate-level Modeling 과 Switch-level Modeling이 있다.

기존에 이미 설계된 모듈들을 가져와 모듈끼리 연결하여 동작하게 하는 방법인데, Gate-level Modeling으로 Gate Primitives를 이용해 미리 정의되어있는 논리게이트 모듈을 사용할 수 있다.

2. 음수의 표현

1) 2의 보수(음수) 체계

: 음수 -N을 N* = 2ⁿ-N의 2진수로 표현(n : bit수)

ex) 4 bit에서 -3을 표현

→ N* = 2⁴-3 = 13 = 1101₂

2) 보수 체계의 범위

- 예를 들어 -9와 7을 2진수로 표현하게 되면, 둘 다 0111₂ 이 나오게 된다.

이렇게 겹쳐지는 부분이 생기므로 범위를 지정하여 그 것만 사용한다.

- MSB 만으로 양수와 음수 구별이 가능하다.

: 음수(1), 양수(0)

3. 수의 변환

1) 2진수의 보수 변환

i) 모든 bit 반전

ii) +1

ex) 0011(= 3)의 보수 변환

i) 1100₂

ii) 1101₂

iii) 검산 : 0010₂ + 1101₂ = (1)0000₂ = 0

∴ 0010₂ 의 보수 = 1101₂

2) 특정 bit만 clear(0으로 변환)

: clear를 원하는 bit에 해당하는 곳에 0, 나머지 bit에 1 넣고 AND 연산

→ 0011₂ & 1101₂ = 0001₂

3) 특정 bit만 set(1로 변환)

: set을 원하는 bit에 해당하는 곳에 1, 나머지 bit에 0 넣고 OR 연산

→ 0011₂ | 0100₂ = 0111₂

4) 특정 bit만 toggle(비트 반전)

: toggle을 원하는 bit에 해당하는 곳에 1, 나머지 bit에 0 넣고 XOR 연산

→ 0011₂ ^ 0100₂ = 0111₂

cf) 위 세 가지는 임베디드에서 자주 사용됨(함수로 만들어 놓고 쓰면 좋다.)

[Testbench]

※ Testbench

: 베릴로그로 구현한 HDL 모델이 올바르게 동작하는지 검증하기 위한 시뮬레이터.

1과 XOR하면, 반전되는 원리를 활용한다.

✅ Testbench work flow

① DUT Instsnce

② 변수선언

③ 입력값 초기화

④ clock 생성

⑤ clock에 따라 테스트 값 입력

⑥ 시뮬레이션

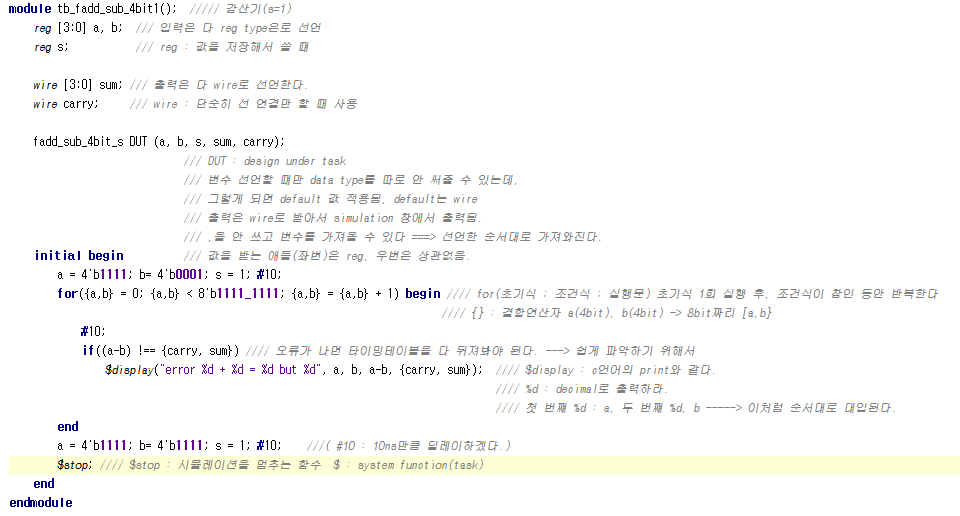

1. 테스트 벤치를 활용한 모듈 테스트

보통 테스트벤치 파일은 따로 만든다.(다른 건, 한 소스 내에 쭉 내려써도 됨)

테스트벤치는 입출력이 없는 모듈

이렇게 test bench가 생성된다.

※ Procedure block

(코딩하는 것들을 묶은 하나의 단위)

- block 내부의 코드는 순차적으로 동작(Verilog는 각 코드들이 동시에 독립적으로 실행)

1) initial

- 모듈이 동작하는 처음에 한 번 실행한다.

2) always @(sensitivity list)

- sensitive list 의 조건이 만족될때마다, always block을 반복한다.

- 종류 → always @ (a, b) : a 또는 b가 변할 때, 반복

always @ (*) : *는 assign에 영향을 미치는 모든 signal

always @ (posedge clk) : rising clk일 때, 반복

always @ (negedge rstn) : falling rstn일 때, 반복

3) begin - end

- sequential executes (선언된 시간이 누적되어 동작)

※ for 문

for(초기식 : 조건식 : 실행문)

: 초기식 1회 실행 후, 조건식이 참인 동안 실행문을 반복한다.

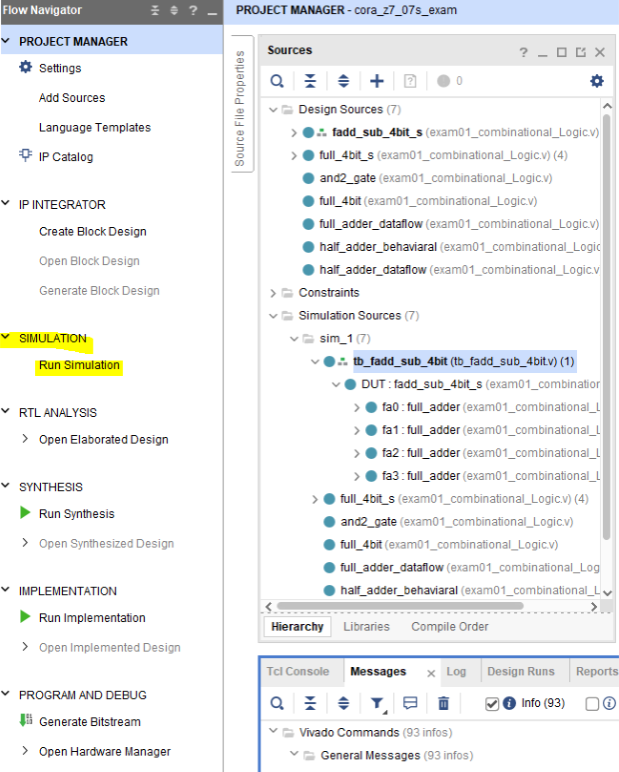

위와 같이 코드를 짜고 Run simulation을 클릭하면,

아래와 같이 timing table이 생성된다.

현재 value 는 default로 설정되어 있고, Radix setting을 바꿔 가독성 좋게 변환시킬 수 있다.

Radix(기수) : 주어진 데이터를 구성하는 기본 요소

▶ : 처음부터 끝까지 시뮬레이션

▶(T) : 우측 설정된 시간까지만 시뮬레이션(10us까지)

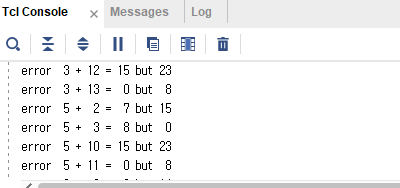

만약 오류가 발생하게 된다면, 처음부터 끝까지 타이밍 테이블을 다 검토해야 한다.

이 과정을 수월하게 하기 위해 에러를 출력하는 코드 추가

$display : c언어의 print와 같은 함수

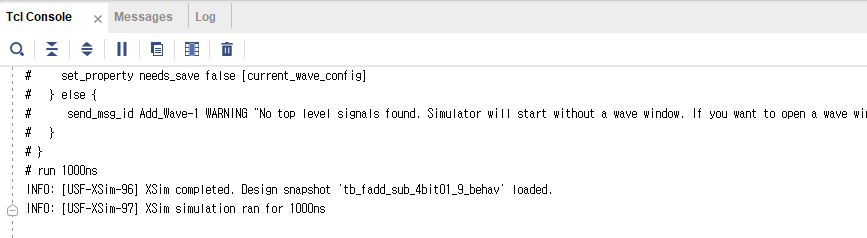

이런 식으로 에러 발생 시, Tcl Console에 출력된다.

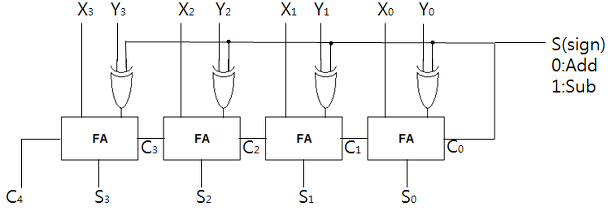

2. 감산기 모듈 테스트

2진수를 보수로 변환하려면 모든 bit를 반전시킨 후 1을 더해야 한다.

- 여기서 모든 bit를 반전시키는 것은 XOR

- 1을 더하는 것은 C0에 1을 주는 것과 같다.

위처럼 s에 1을 넣어주고 실행하면, 다음과 같이 시뮬레이션 결과가 출력된다.

※ Overflow

- 2의 보수 체계를 사용하고 있을 때, 해당 범위를 넘어서는 값이 입력되면

표현할 수 있는 한계를 넘어 계산 결과가 달라지는 경우를 말한다.

- 보통 양수+양수 or 음수+음수일 때 발생

- overflow 알아내는 법

① 두 입력의 msb = 0, 출력의 msb = 1

② 두 입력의 msb = 1, 출력의 msb = 0

- 우리는 4bit 2의 보수 체계(-8~7)를 사용하고 있기 때문에 계산 결과가 다르게 출력된다.

※ 감산기의 비교기 역할

- 감산기에서 뺄셈 결과가 음수가 아닐 때, carry가 발생한다.

→ carry = 1 이면, a가 b보다 크거나 같다.(비교기 역할)

[Delay]

회로를 설계하고 시뮬레이션까지 완벽하게 했는데, 막상 실제로 회로를 만들면 수많은

오류가 발생하며 대부분의 문제들이 Delay로 인해 발생한다.

- 시뮬레이션은 모든 딜레이가 0인 이상적인 상태로 이루어 진다.

1. PDT(Propagation Delay Time)

= 전파 지연 시간

1) FPGA의 모든 Gate는 CMOS로 이루어져 있다.

반도체의 특성 상, normal 상태에서는 공핍층이 형성되어 있고 약 0.7V의 전위차를 갖는다.

신호가 전달되기 위해서는 해당 전위차만큼 충전될 때까지 시간이 필요하며, 이 시간만큼 Delay가 발생하게 된다.

ex) Timing table 상 pulse가 수직이 아닌 대각선으로 상승, 하강

: rising time, falling time

2) 실제로 회를 구동시켜보면, gate 1개를 통과할 때마다 delay가 발생한다.

각 출력까지 gate 수는 서로 차이가 있고 이로 인해 pdt가 발생하고

결국 glitch(잘못된 신호)가 출력된다.

2. Jitter

: 디지털 펄스 신호에서 원하는 이상적인 신호와

실제 신호 간의 시간축에서의 차이

→ 쉽게 말하자면, 노후화 또는 인가하고자 하는

신호가 많아 노이즈가 끼게 된 것.

3. Set-up time / Hold time

: 데이터가 결과를 출력할 때까지 안정적으로 유지되고 있어야 한다.

1) Set-up time

: rising하기 전에 미리 데이터가 준비되어야 하는 시간

2) Hold time

: rising 이후 data가 유지되고 있어야 하는 시간

4. Skew

: 모든 clock은 Clock source와 같은 거리에 존재하는 것이 아니기 때문에

서로간의 오차가 발생하게 되고 이를 Skew라고 부른다.

이와 같은 Skew를 방지하기 위해, H tree drawing 기법을 사용한다.

※ 결론

Period > Gate delay + rising time + Jitter + Set-up time + Homd time + Skew

- rising time은 Set-up time & Homd time 에 포함되므로 제외 가능

<Delay 예시>

시뮬레이션 돌릴 때만 딜레이가 걸린다.

(실제 회로로 만들어졌을 때는 딜레이 적용 안 됨.)

딜레이가 시뮬레이션에 적용된 모습

딜레이가 추가되니, 에러도 많이 나온다.

→ 딜레이가 있기 때문에, 결과가 출력되는 시간을 좀 더 여유있게 줘야 한다.

20ns 로 여유롭게 데이터를 읽을 시간을 주었고, 에러없이 잘 출력되었다.

'# Semiconductor > [Semicon Academy]' 카테고리의 다른 글

| [Harman 세미콘 아카데미] 3일차 - Cora z7 setting, Decoder (0) | 2023.06.21 |

|---|---|

| [Harman 세미콘 아카데미] 3일차 - 가산기,비교기, 인코더/디코더 (0) | 2023.06.21 |

| [Harman 세미콘 아카데미] 1일차 - Half adder, Full adder (0) | 2023.06.19 |

| [Harman 세미콘 아카데미] 1일차 - FPGA board (0) | 2023.06.19 |

| [Harman 세미콘 아카데미] 1일차 - VIVADO setting (0) | 2023.06.19 |