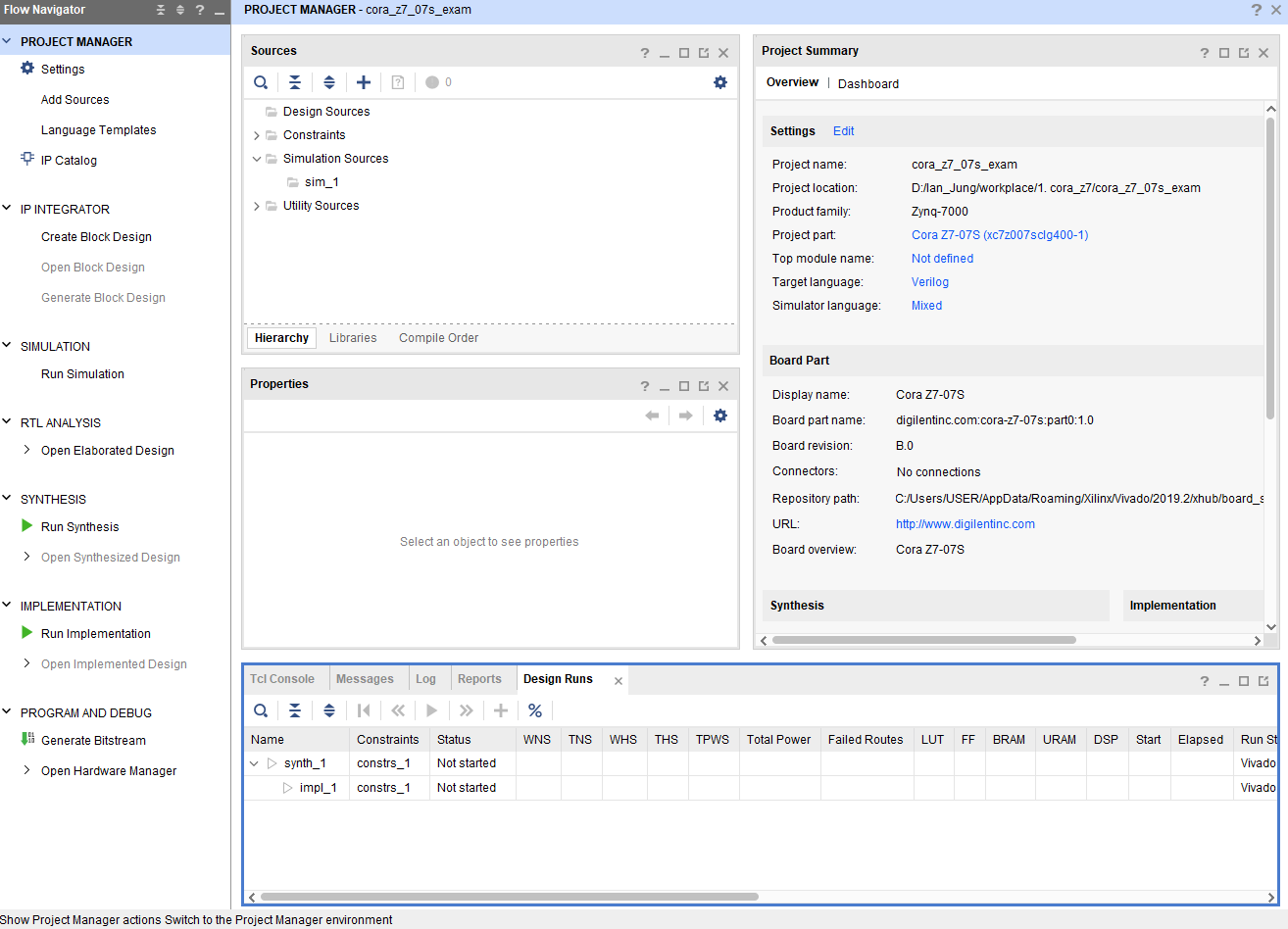

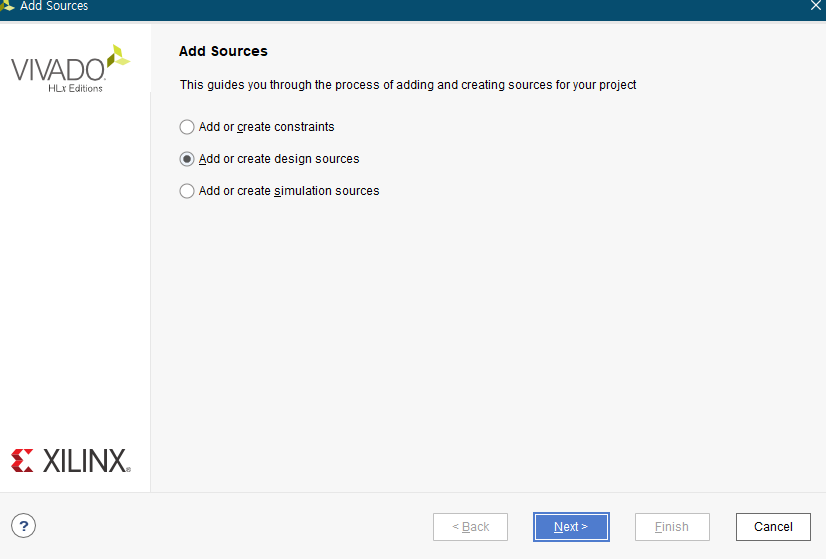

[Source 생성]

Source 탭에서 + 표시를 클릭

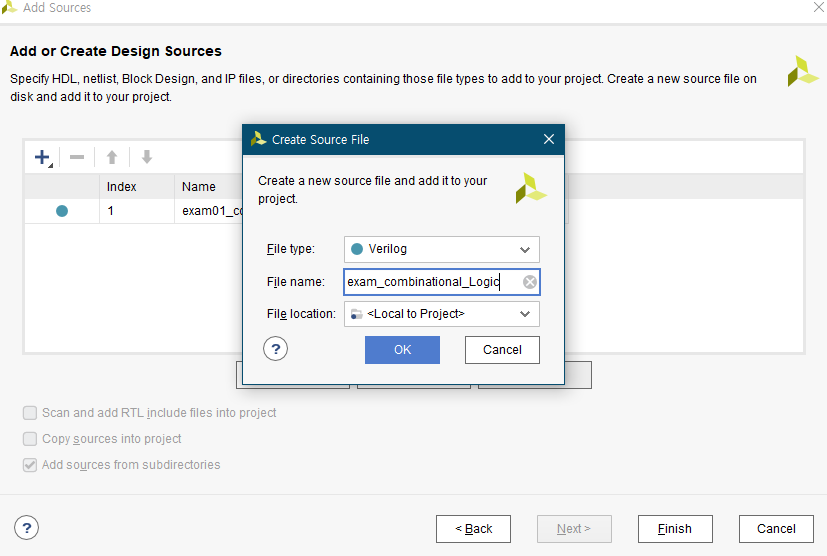

첫 source 생성이므로, create file 클릭하고 파일명 설정

모듈의 input와 output을 설정해주면,

위와같이 모듈명과 변수들이 자동으로 선언된다.

[Modeling 방법]

Modeling 방법은 총 세 종류가 있다.

1. Gate-level Modeling(=Structural Modeling)

: 어떤 특정한 구조나 기술을 나타내지 않는 상위 추상화 레벨(매우 중요한 회로, 블록 표현)

2. Data-flow Modeling

: 사용한 컴포넌트와 컴포넌트 간의 상호연결 구조가 분명히 기술되는 하위 추상화 레벨

(특정 라이브러리/패키지의 개별 게이트나 플립플롭의 사용을 지정할 수 있음)

3. Behavior Modeling

: 상위와 하위 중간인 중간 추상화 레벨(RTL : Register Transer Level)

<특징>

1. Gate level Modeling은 가장 구체적이고 추상도 lv가 낮다.

Behavior Modeling은 가장 추상적이며 추상도 lv가 높다.

Data-flow Modeling은 중간적인 성격을 띈다.

2. Combinational Modeling에는 Gate-level Modeling, Data-flow Modeling

Sequential Modeling에는 Behavior Modeling이 사용된다.

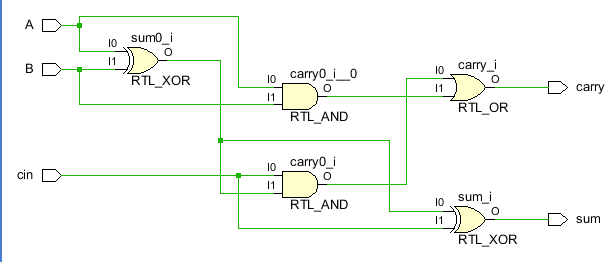

[Half_adder]

※ Half_adder

: 반가산기라고도 하며, 1bit 의 값을 계산하는데 사용된다.

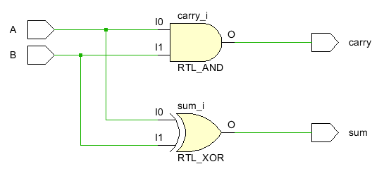

1. Gate level modeling

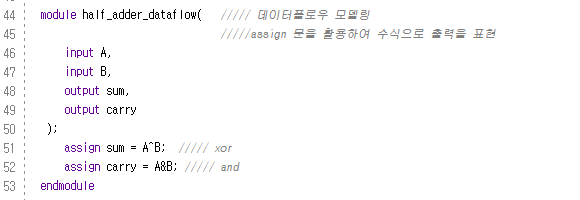

2. Data flow modeling

- assign 문과 비트연산자를 사용하여 출력을 표현한다.

※ assign → 좌변 : 값을 할당받고자 하는 변수, 우변 : 왼쪽 변수에 할당해줄 값

즉, 우변의 값에 따라 좌변의 값이 좌우된다.

cf) 연속적 할당문(continuous assignment)

: assign 문법을 사용하여 combinational logic을 선언하는 문법

(data type : wire)

절차적 할당문(procedural assigment)

: always, initial 등의 문법을 사용하여 logic을 선언하는 문법

(data type : reg, wire 등)

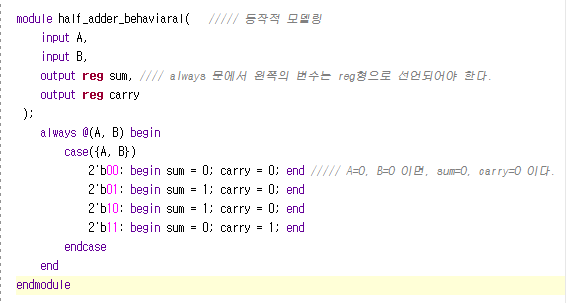

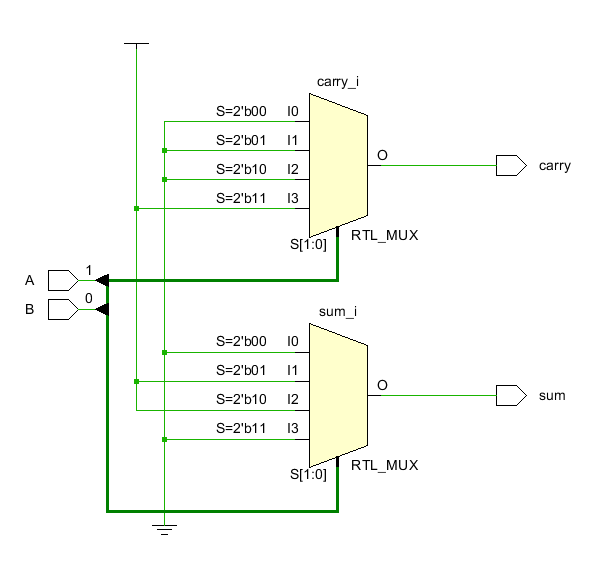

3. Behavior Modeling

- Behavior Modeling 에서는 Gate가 아닌 MUX(nut의 한 종류)가 사용되었다.

FPGA에서는 게이트가 생성되지 않기에, 위와 같은 MUX로 회로가 생성된다.

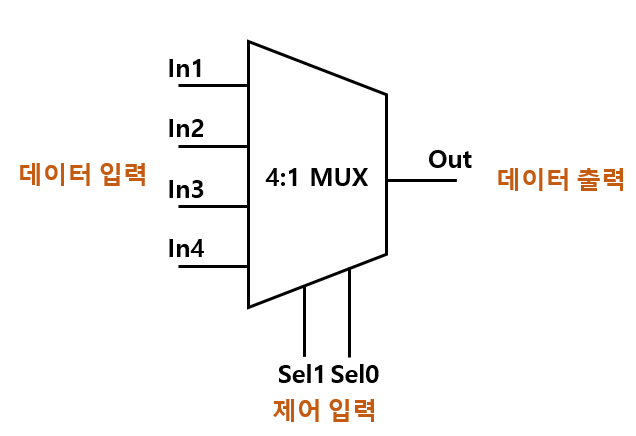

- MUX(Multiplexer)

: 데이터 선택기

제어 입력은 data input 중에서 하나를 선택하여 출력단과 연결하는 역할을 한다.

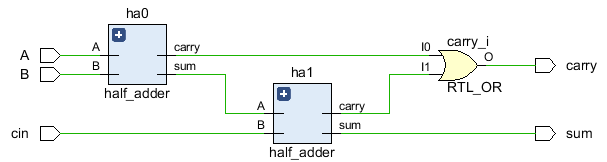

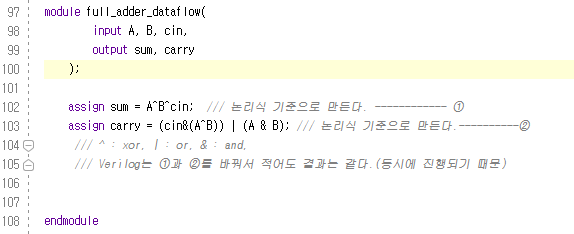

[Full_adder]

※ Full_adder

: 전가산기라고도 하며, 1bit 이상의 값들을 계산하는데 사용된다.

1. Combinational Modeling

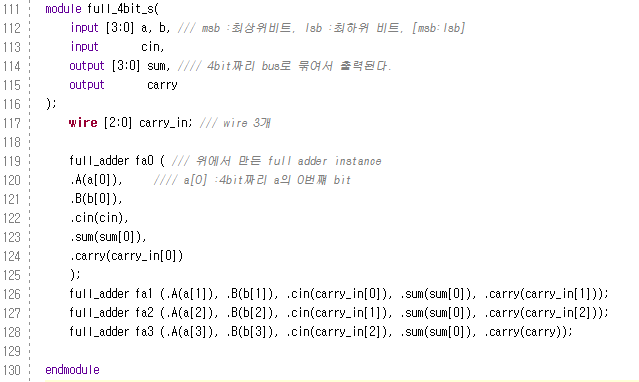

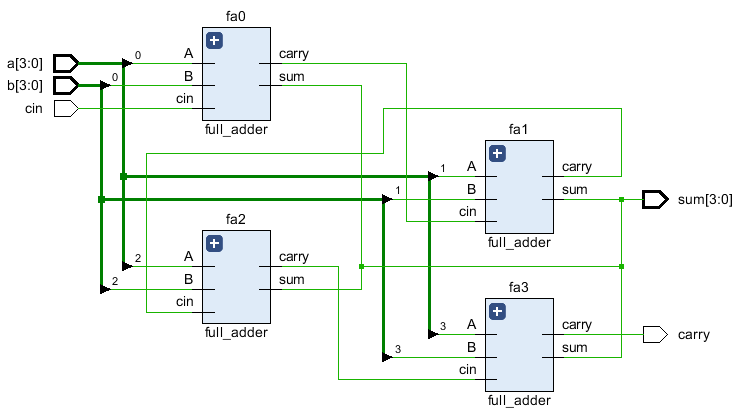

2. Gate level Modeling

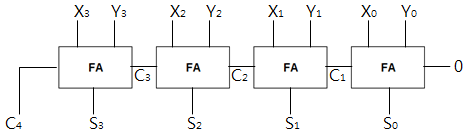

[Parallel-adder/subtracter]

위의 가산기는 1bit의 출력만 다뤘다면,

Parallel-adder/subtracter(병렬 감가산기)는 가산기를 병렬로 연결해 1bit 이상의 출력을 다룰 수 있다.

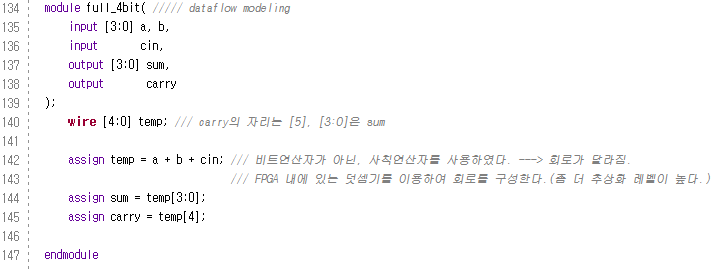

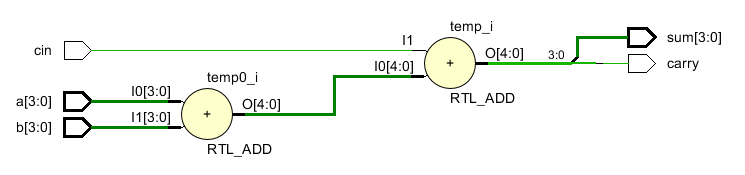

1. Combinational Modeling

2. Data flow modeling

'# Semiconductor > [Semicon Academy]' 카테고리의 다른 글

| [Harman 세미콘 아카데미] 3일차 - Cora z7 setting, Decoder (0) | 2023.06.21 |

|---|---|

| [Harman 세미콘 아카데미] 3일차 - 가산기,비교기, 인코더/디코더 (0) | 2023.06.21 |

| [Harman 세미콘 아카데미] 2일차 - 보수체계, Testbench, Delay (0) | 2023.06.20 |

| [Harman 세미콘 아카데미] 1일차 - FPGA board (0) | 2023.06.19 |

| [Harman 세미콘 아카데미] 1일차 - VIVADO setting (0) | 2023.06.19 |