[개요]

시스템 반도체를 설계하는 언어는 대표적으로 2가지가 있다.

1. Velilog

: 전자 회로 및 시스템에 쓰이는 하드웨어 기술 언어(HDL, Hardware Description Language)

회로를 설계할 때 사용하는 언어로, 하드웨어는 순차적으로 돌아가지 않고

Clock에 따라서 동시에 동작하므로 시간과 동시성(concurrency)을 표현할 수 있고

컴파일 과정이 일반적인 프로그래밍언어와 다르다.

대부분의 기업, 현직자, 유럽을 제외한 국가에서 많이 사용된다.

2. VHDL(VHSIC Hardware Description Language)

: 디지털 회로의 설계 자동화에 사용하는 하드웨어 기술 언어이며,

주로 대학 또는 연구원, 유럽에서 많이 사용된다.

[VIVADO 기본 세팅]

VIVADO를 처음 시작하면 위와 같은 화면이 나타난다.

우리는 이제부터 프로젝트를 만들어야 하므로,

Create Project를 클릭한다.

next 클릭

프로젝트명을 설정하고, 파일이 저장될 경로도 설정해 준다.

tip) D드라이브에 저장하는 것이 좋다.(윈도우 날라가도 데이터 보존됨.)

우리는 시스템 반도체 설계를 위해 사용하므로 RTL Project 로 생성한다.

- RTL(Register-transfer level)

: 레지스터와 로직회로를 이용하여 Synchronous 디지털 회로를 설계하는 레벨

아직 소스 파일을 생성할 것이 아니므로, next 클릭

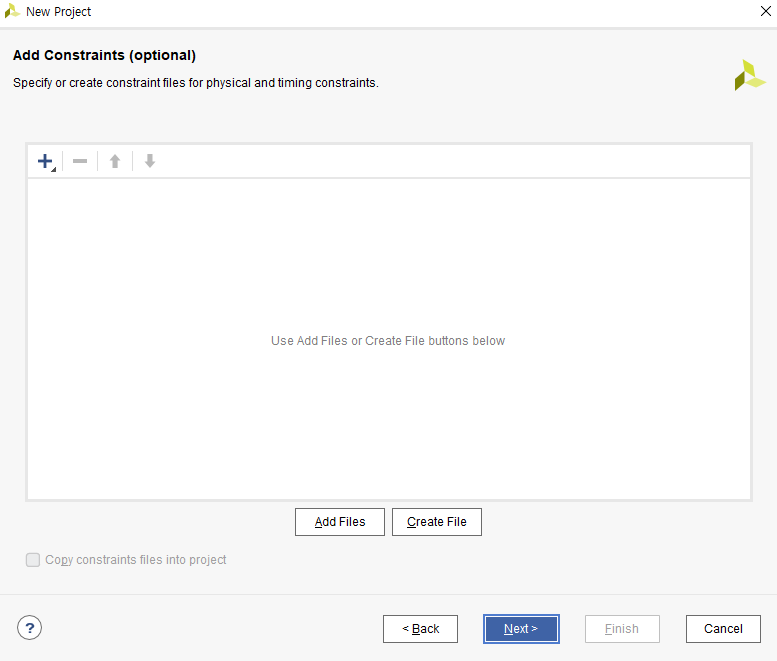

next 클릭

Parts : FPGA 칩을 뭘 쓸 것이냐?

Boards : 보드는 어떤 것을 쓸 것이냐?

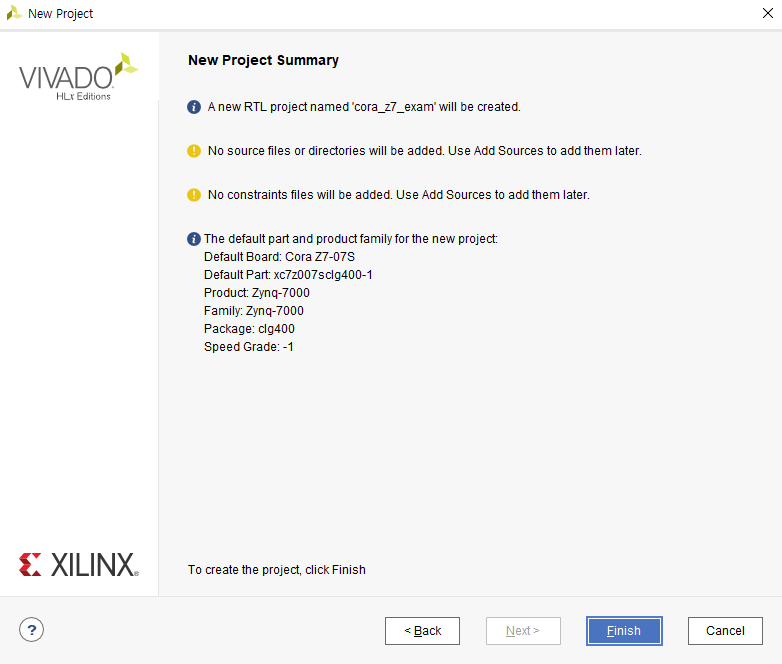

우리는 Cora Z7-07S 라는 board를 사용할 것이므로 board 배너에서 cora를 검색하여 선택

cf) 검색을 해도 보드가 안 뜨는 경우, Update Board Repositories 클릭하여 업데이트

그래도 안 되면, 최신 버전 다운로드

Finish

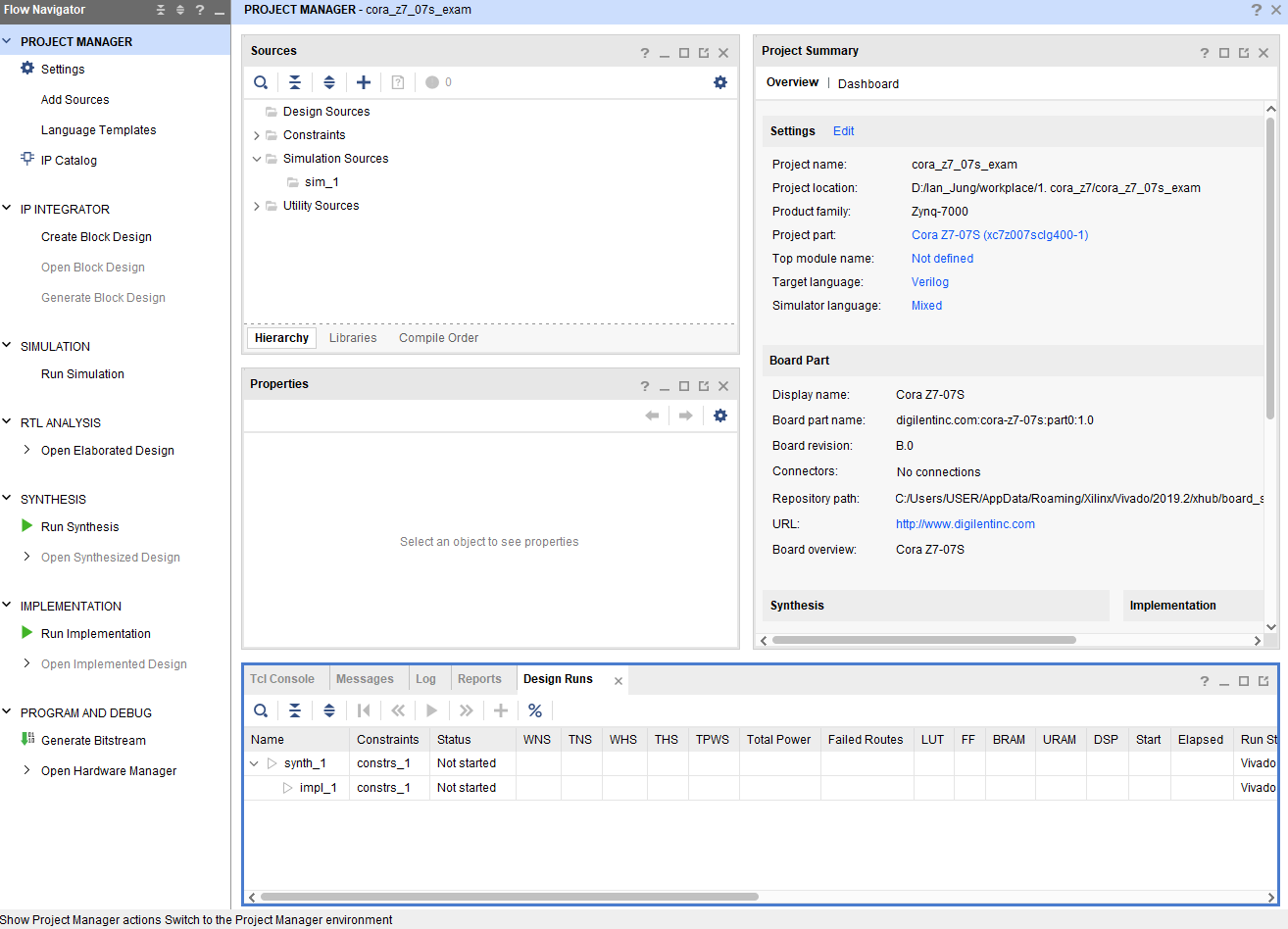

셋팅이 완료되면 이런 창을 볼 수 있다.

'# Semiconductor > [Semicon Academy]' 카테고리의 다른 글

| [Harman 세미콘 아카데미] 3일차 - Cora z7 setting, Decoder (0) | 2023.06.21 |

|---|---|

| [Harman 세미콘 아카데미] 3일차 - 가산기,비교기, 인코더/디코더 (0) | 2023.06.21 |

| [Harman 세미콘 아카데미] 2일차 - 보수체계, Testbench, Delay (0) | 2023.06.20 |

| [Harman 세미콘 아카데미] 1일차 - Half adder, Full adder (0) | 2023.06.19 |

| [Harman 세미콘 아카데미] 1일차 - FPGA board (0) | 2023.06.19 |