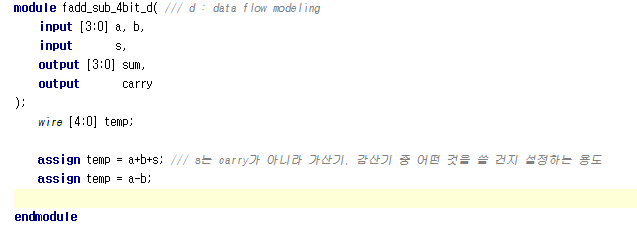

[가산기]

1. 가산기를 Data-flow modeling으로 설계

위 식은 조건연산자를 활용하여 작성할 수도 있다.

※ 조건연산자

Q = 조건식 ? A : B;

i) 조건식이 참(1)일 경우,

Q = A

ii) 조건식이 거짓(0)일 경우,

Q = B

2. 가산기 모듈을 테스트 벤치에 인스턴스

: 변수는 이전과 같으므로 DUT 값만 변경해주면 된다.

cf) 가독성을 좋게 하기 위해 4자리마다 _를 붙여주면 좋다.

→ 9'b1_1111_1111

[비교기]

1. 1-bit 비교기

1) 논리 연산자로 i-bit 비교기 설계

assign 문을 사용하여 설계하였지만,

논리연산자를 사용하면 구조적 모델링과 별 차이가 없게 된다.

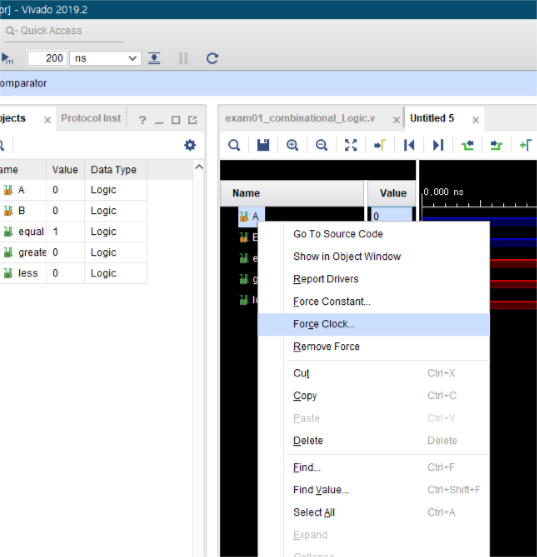

※ Force clock

시간의 흐름에 따라서 값을 지정해줄 수 있는 기능이다.

각 bit별로 leading과 trailing, period를 설정해주면 된다.

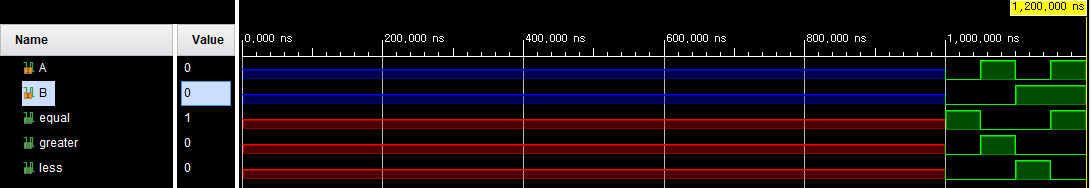

2) 조건 연산자를 활용한 1-bit 비교기 설계

VIVODO 내부에 저장되어 있는 RTL 로 표현된다.

논리 gate로 표현될 경우, bit 수가 올라감에 따라 회로는 점점 더 복잡해지고 설계도 따로 해줘야 한다.

하지만, 위처럼 저장되어 있는 RTL로 표현된다면, input의 bit 수만 변경해주면 된다.

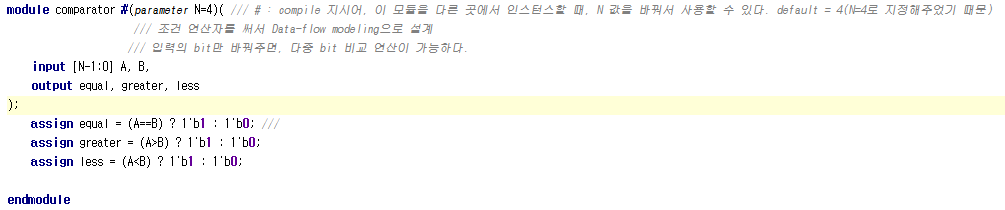

3) Parameter의 활용

※ Parameter

① 미리 parameter를 선언해놓으면, 추후에 instance할 때 N값만 변경시키면

다른 bit 수의 회로로사용이 가능하다.

→ defparam 문, module instance 문의 parameter overriding에 의해 변경 가능

② Variable /.Net 범주에는 속하지 않는 상수값

cf) # - Delay(할당문 등에 사용)

- Parameter를 변경하는 용도(compiler 지시어)

[Decoder & Encoder]

1. 기본 개념

1) Decoder : code → signal 로 변환(압축 해제기)

(En)coder : signal → code 로 변환(압축기)

CODEC : Encoder의 'CO' + Decoder의 'DEC'

2) 원리

입력 →→ Encoder →→ Decoder →→ 출력

signal code signal

ex) 4개의 입력 → Encoder → 2 개의 code로 전달(0 또는 1)

이렇게 전달되면, 배선의 길이 등이 줄어들어 비용이 절감되고 디지털 코드로 전송되기 때문에

보안성도 갖추게 된다.

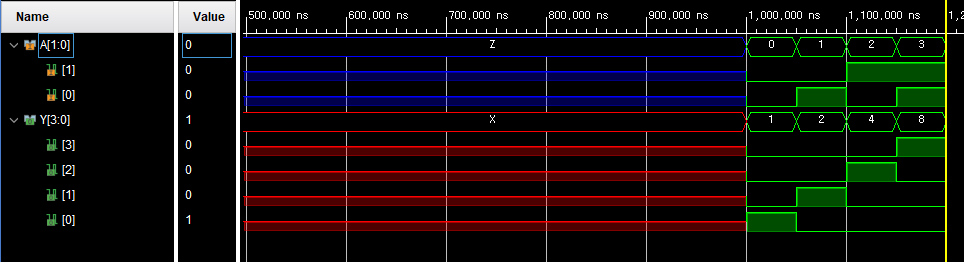

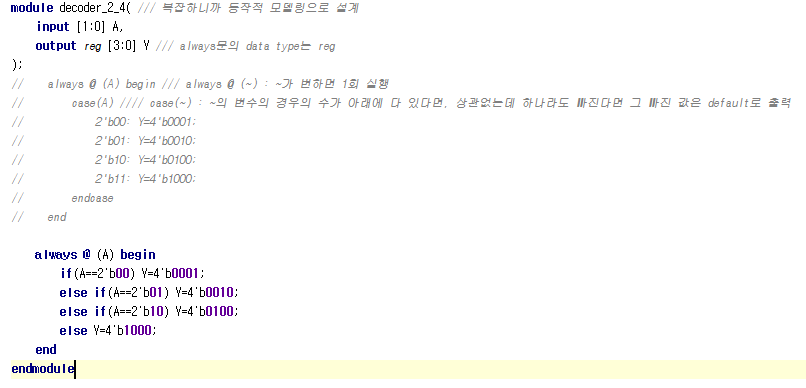

2. Decoder

※ 조건 연산자

conditional_expresstion = expression1 ? expression2 : expression3

i) ex1 = 1(참), 좌변의 변수에 ex2를 할당해 준다.

ii) ex1 = 0(거짓), 좌변의 변수에 ex3를 할당해 준다.

iii) ex1 = x 또는 z, ex2와 ex3를 비트끼리 비교해서 같은 값이면 좌변에 할당.

다른 값이면 좌변에 x를 할당.

3. Decoder(enable 추가)

: enabla에 따라서 output 값의 출력 여부가 정해진다.

en = 1이면 연산된 값이 출력되고 en = 0이면 0이 출력된다.

'# Semiconductor > [Semicon Academy]' 카테고리의 다른 글

| [Harman 세미콘 아카데미] 4일차 - 7_segment로 디코더 회로 출력하기 (0) | 2023.06.22 |

|---|---|

| [Harman 세미콘 아카데미] 3일차 - Cora z7 setting, Decoder (0) | 2023.06.21 |

| [Harman 세미콘 아카데미] 2일차 - 보수체계, Testbench, Delay (0) | 2023.06.20 |

| [Harman 세미콘 아카데미] 1일차 - Half adder, Full adder (0) | 2023.06.19 |

| [Harman 세미콘 아카데미] 1일차 - FPGA board (0) | 2023.06.19 |