[FPGA board]

1. Board setting

: 설계한 회로를 board에 programing하기 위해서는

입출력 변수들을 board의 입출력 단자에 연결해주어야 하고

그러기 위해서는 board에 장착된 FPGA chip의 연결 정보를 알아야 한다.

→ XDC file을 다운받아 vivado에서 programing

1) XDC File 다운받기 & 불러오기

※ Cora z7 board 관련 링크

https://digilent.com/reference/programmable-logic/cora-z7/start

Cora Z7 - Digilent Reference

digilent.com

※ C언어에서 사용 가능한 파일 경로

사용 가능 : 영어 대문자/소문자, 숫자(맨 앞에는 오면 안 됨), _(under bar)

사용 불가 : 한글, 공백(띄어쓰기)

copy check를 안 하면, 현재 프로젝트로 인해 프로그래밍된 보드를 다른 프로젝트에서도 같이 공유하게 됨.

해당 보드 프로그래밍의 목적은 입력된 code가 decoder로 변환되어 제대로 출력되는지 확인하기 위함이다.

→ button을 눌러 입력 신호 전달 & led로 변환된 신호 출력

따라서 입출력 변수를 해당 board의 입출력 포트와 연결해주는 작업이 필요하다.

i) btn[0] → A[0], btn[1] → A[1], ---------- (입력 포트 연결)

ii) led0_b → Y[0], led0_g → Y[1], ---------- (출력 포트 연결)

led1_b → Y[2], led1_g → Y[3]

2) Flow Navigator

① Project Manager

: 프로젝트 관련 설정 및 소스 코드 관리, Xilinx IP 관리 등을 할 수 있다.

프로젝트 관련 설정들이 다 모여있는 곳.

② IP integrator

: IP를 가져다 블록 다이어그램을 서로 연결하는 방식으로 전체 디자인을 구성하고 싶을 때 사용한다.

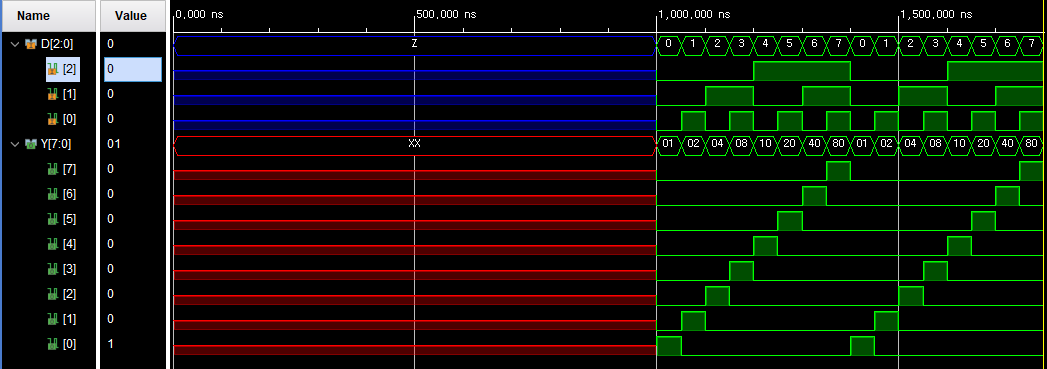

③ Simulation

: 작성된 코드를 RTL 시뮬레이션할 때 사용한다.

Timing table을 기반으로 작성한 코드가 완벽한 지 확인할 수 있다.

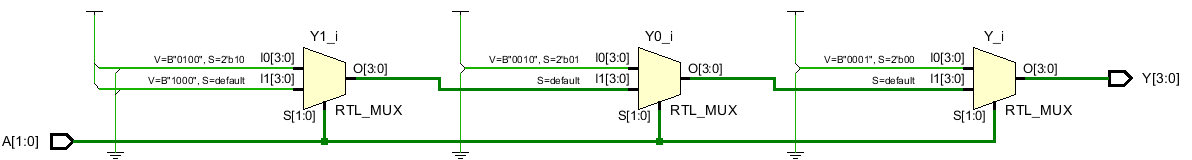

④ RTL Analysis

: 툴이 자동으로 RTL을 분석해서 Schematic을만들고, 취약점을 알려준다.

취약점은 DRC(Design Rule Check)있으며, 회로가 잘 동작하지 않을 때 체크해볼 것.

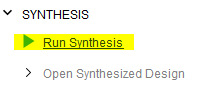

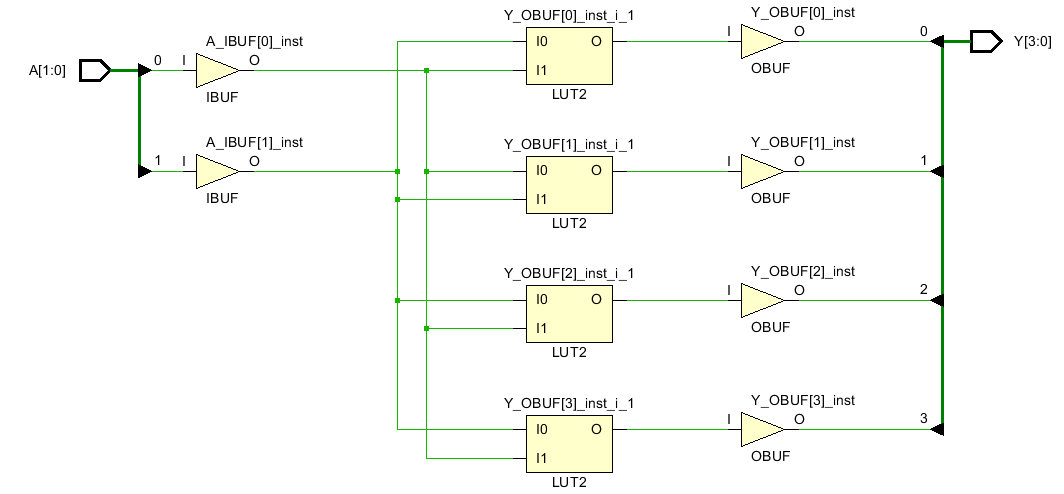

⑤ Synthesis

: RTL을 gate-level로 바꾸는 작업(=합성)

RTL을 FPGA 내부에 있는 LUT 등 각종 모듈로 변환하는 단계

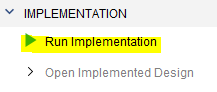

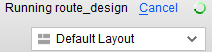

⑥ Implementation

: 입출력을 실제 FPGA의 소자들과 연결하는 과정

즉, 어떤 게이트가 필요하고 어떻게 연결되어야 하는지 결정하는 단계이다.

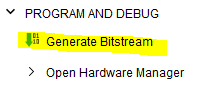

⑦ Program & Debug

: 위에서 준비된 것들을 bitstream으로 만든 뒤, FPGA에 구현하는 단계

3) Board Programing

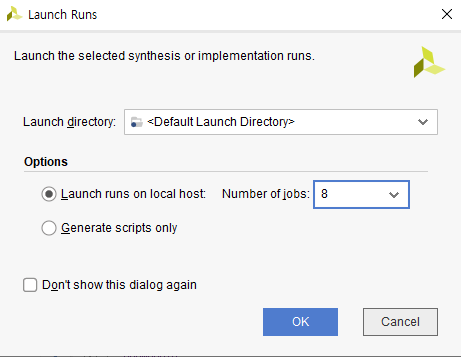

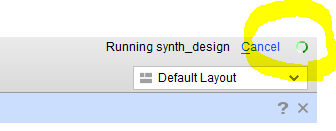

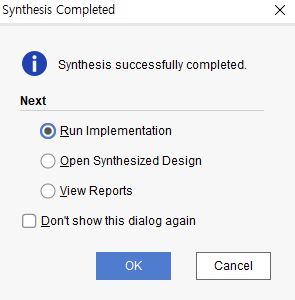

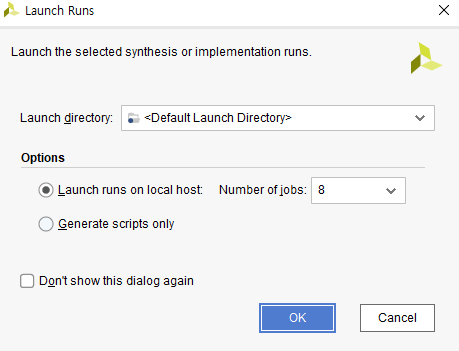

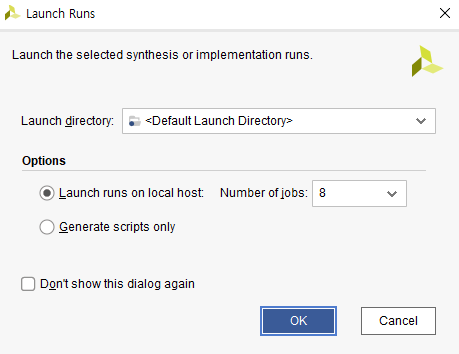

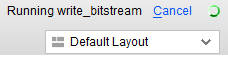

① Synthesis

연산을 수행할 Core 수를 설정해준 뒤 ok를 누르면 합성을 시작한다.

Number of jobs = core 수 설정

core 수가 많을수록 합성이 빨리 진행된다.

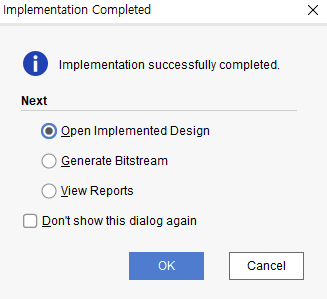

② Implementation

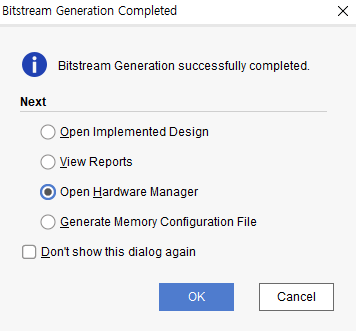

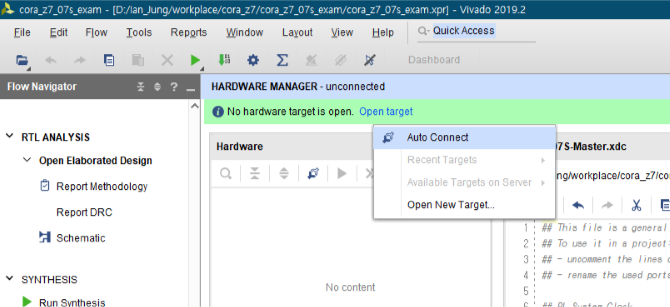

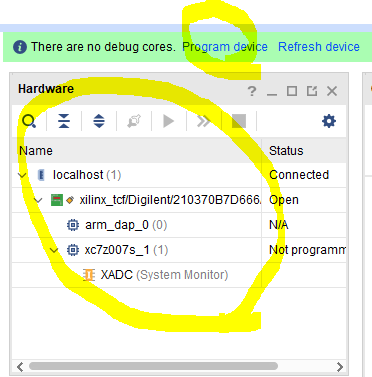

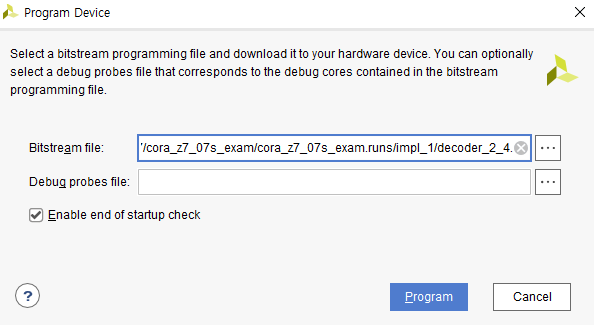

③ Program & Debug

program device 클릭

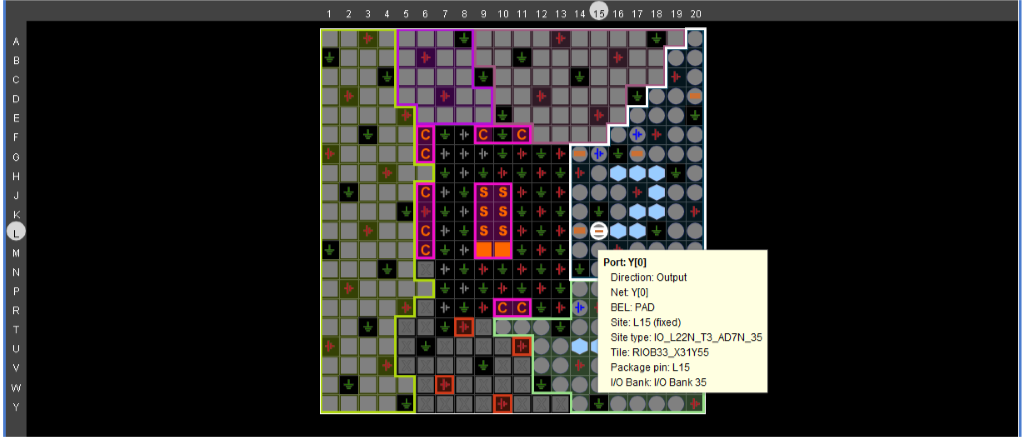

아래 마킹된 부분에서 해당 보드의 정보들을 볼 수 있다.

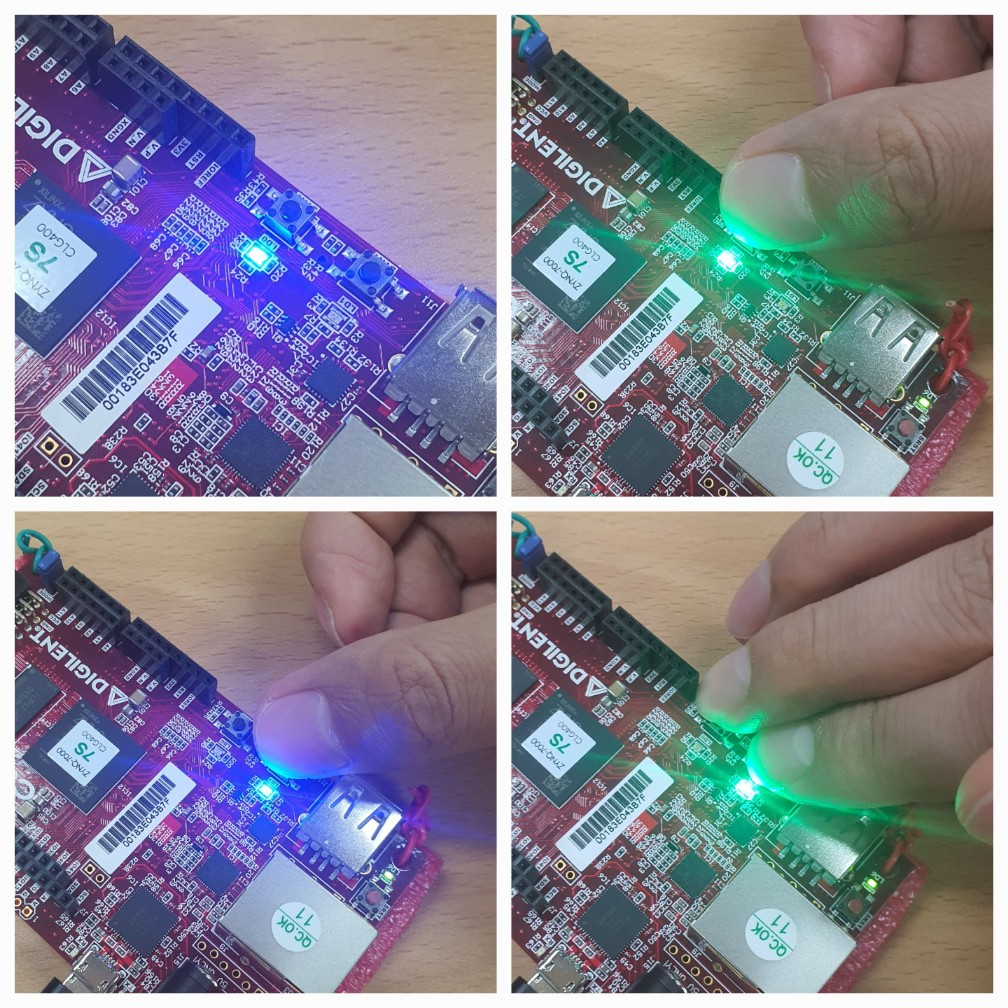

④ 보드 살펴보기

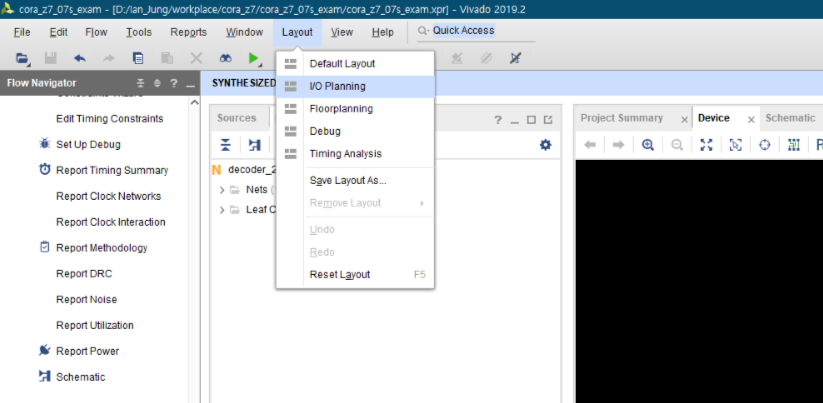

Layout → I/O planning 클릭하면 아래와 같이 FPGA chip의 plan을 볼 수 있다.

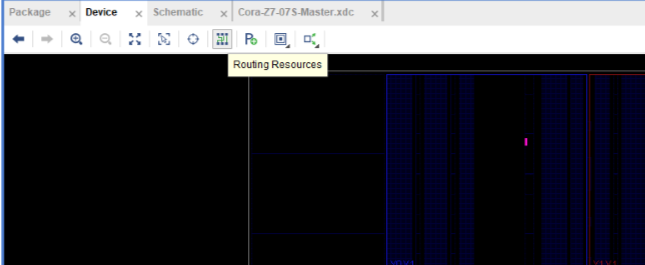

해당 버튼을 클릭하고 확대하면 FPGA board의 전체적인 회로도를 볼 수 있다.

④ 설계한 Decoder 회로를 board에 적용

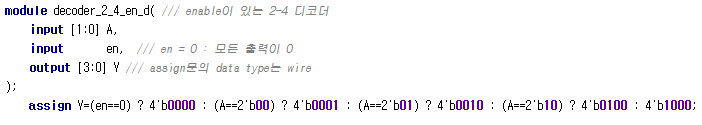

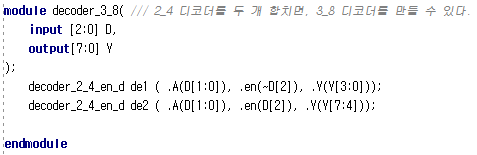

[2x4 Decoder로 3x6 decoder 만들기]

위의 2x4 Decoder를 Instance하여 3x8 Decoder 코드 작성

'# Semiconductor > [Semicon Academy]' 카테고리의 다른 글

| [Harman 세미콘 아카데미] 4일차 - Encoder 설계, MUX, LUT (0) | 2023.06.22 |

|---|---|

| [Harman 세미콘 아카데미] 4일차 - 7_segment로 디코더 회로 출력하기 (0) | 2023.06.22 |

| [Harman 세미콘 아카데미] 3일차 - 가산기,비교기, 인코더/디코더 (0) | 2023.06.21 |

| [Harman 세미콘 아카데미] 2일차 - 보수체계, Testbench, Delay (0) | 2023.06.20 |

| [Harman 세미콘 아카데미] 1일차 - Half adder, Full adder (0) | 2023.06.19 |