[Encoder]

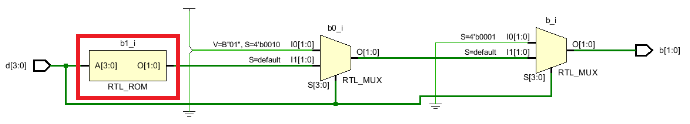

schematic을 생성하면, ROM을 포함하여 생성된다.

(4-bit이므로 ROM 내부에 16개의 메모리가 생성됨)

우리가 정해준 4개 빼고 나머지 12개에는 다 2’b11(조건연산자의 가장 마지막 값)을 저장해버린다.

회로만 좀 낭비될 뿐, 문제는 없다.

(입력이 많아질수록 더 많은 메모리가 많이 낭비됨)

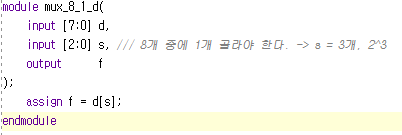

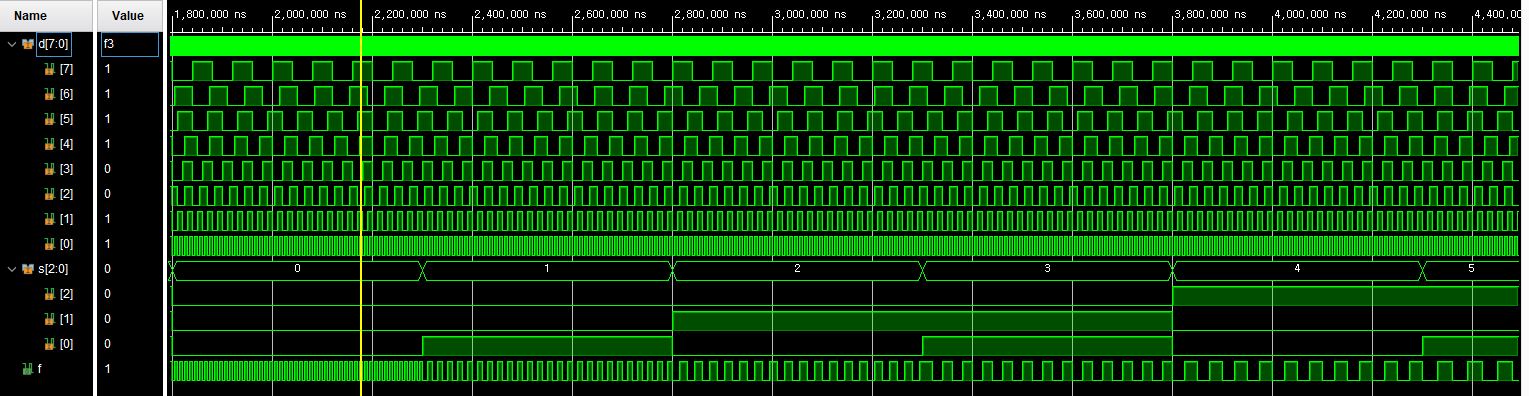

[MUX]

MUX란?

= 'Multiplexer' or 'Selector'

여러 개의 입력 신호 중에서 하나를 선택하여 출력 선에 연결하는 조합 회로.

(FPGA에서 필수적이며 정말 많이 사용된다.)

디코더와 비슷하지만 다르다.

→ 들어오는 신호 중에 하나 골라서 출력(압축이 아닌, 선택)

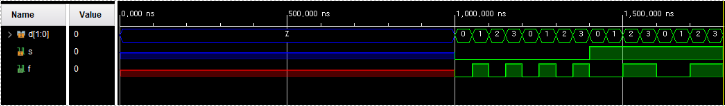

2x1 MUX

1) Structure Modeling

2) Dataflow modeling

[LUT]

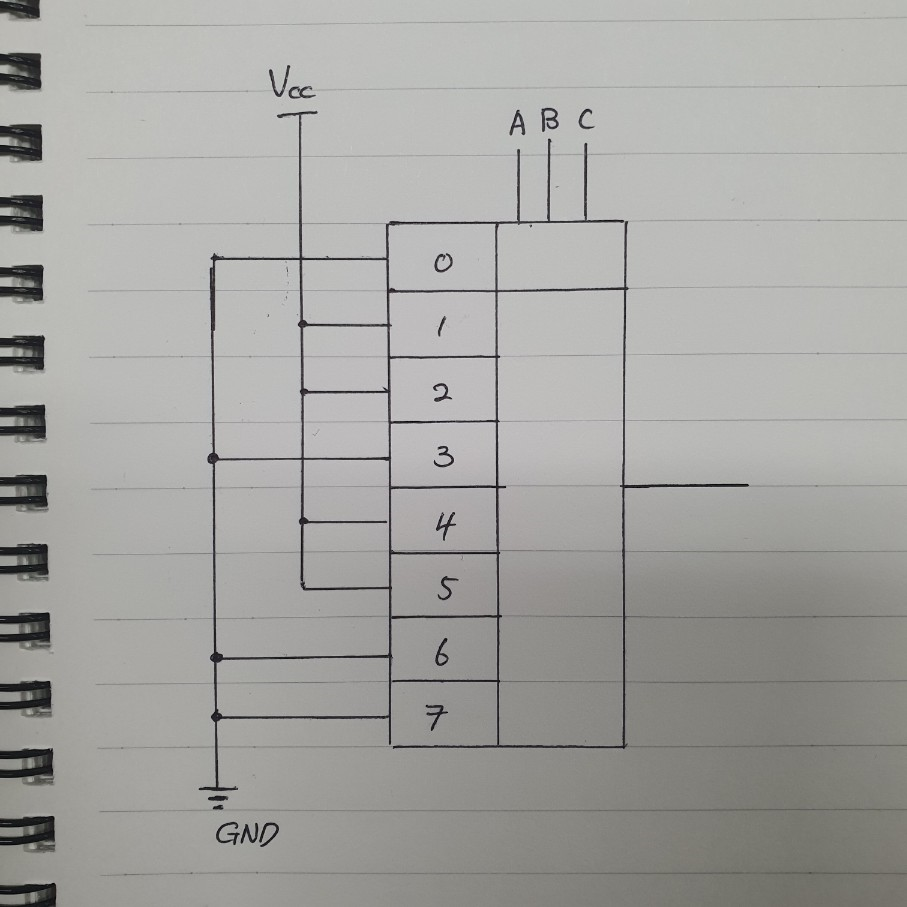

LUT(Look-up Table)

f(A, B, C) = m∑(1, 2, 4, 5)

위 equation을 회로로 표현하려면,

Karnough map(카르노 맵) Boolean Algebra(불 대수식)을 이용하여 간소화하는 과정이 필요하다.

→ 복잡하고 시간도 많이 걸림. 귀찮아.

하지만, LUT이라는 개념의 등장으로 위와 같은 복잡한 방법은 더 이상 사용하지 않아도 된다.

LUT은 주어진 연산에 대해 미리 계산된 결과들의 집합이며, 일종의 메모리로 볼 수 있다.

이와 같은 LUT을 사용하여 회로를 설계하게 되면, 설계 시간이 단축되는 것은 물론이고 게이트 수 때문에 발생하는 pdt로 인해 생성되는 Glitch 생성률을 현저히 낮출 수 있다.

'# Semiconductor > [Semicon Academy]' 카테고리의 다른 글

| [Harman 세미콘 아카데미] 5일차 - Sequential Logic(LATCH, FF) (0) | 2023.06.23 |

|---|---|

| [Harman 세미콘 아카데미] 5일차 - Demux, 코드변환기 (0) | 2023.06.23 |

| [Harman 세미콘 아카데미] 4일차 - 7_segment로 디코더 회로 출력하기 (0) | 2023.06.22 |

| [Harman 세미콘 아카데미] 3일차 - Cora z7 setting, Decoder (0) | 2023.06.21 |

| [Harman 세미콘 아카데미] 3일차 - 가산기,비교기, 인코더/디코더 (0) | 2023.06.21 |