[Squential Logic]

Squential Logic

= 순차 논리 회로

- Combinational Logic과 달리 feedback 기능이 있다.

#feedback : 출력이 입력에 영향을 줌.

- Time dependent(clock에 의해 좌우된다.)

.- 회로는 Latch 또는 Flip-flop로 구성된다.

| 공통점 | 차이점 | |

| Latch | 상태 기억 소자 - 현재 상태를 기억하고 유지한다 (HOLD) - 적절한 시점이 되었을 때, 그 기억을 바꿀 수 있어야 한다. (Triggered 방식) |

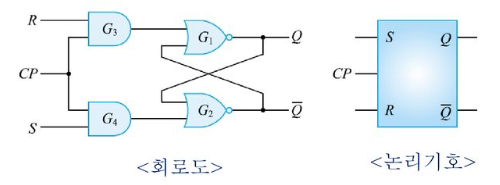

Level-triggered : clk가 특정한 값을 가지고 있을 때 동작 |

| Flip-flop | Edge_triggered : clk이 0→1 또는 1→0이 되는 시점에 동작 |

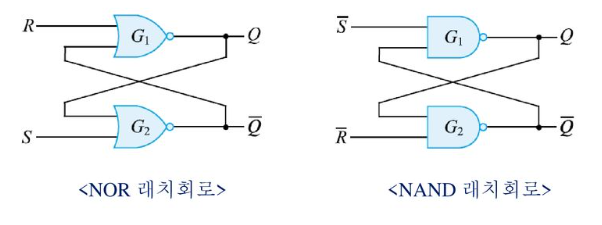

[LATCH]

메모리의 시작이기도 한 이 회로는 실제로는 쓸모없는 회로이다

왜 와이?

예시)

NOR LATCH에서 Q=Q'=0, R=S=0이면,

Q : 0 → 1 → 0 → 1

Q' : 0 → 1 → 0 → 1

위와 같이 '발진'한다. → 부정(Q=Q'=0이라서 부정이 아님)

주기라도 일정하며, clock으로라도 사용하겠는데, 그러지도 않음.

굳이 쓴다면, 스위치에서 바운싱 제거용으로...? 굳이..?

11의 입력은 제거하고, 00의 입력은 en이 담당하여 메모리 기능을 할 수 있도록 한다.

<LATCH 회로 만들기>

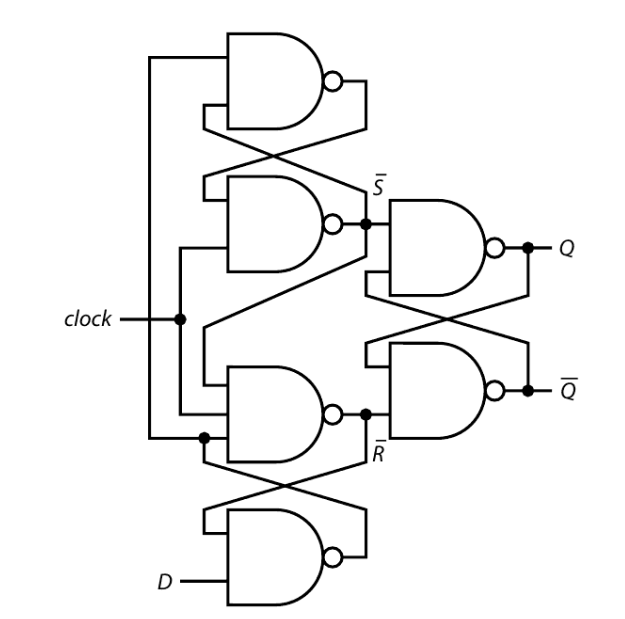

[FLIP-FLOP]

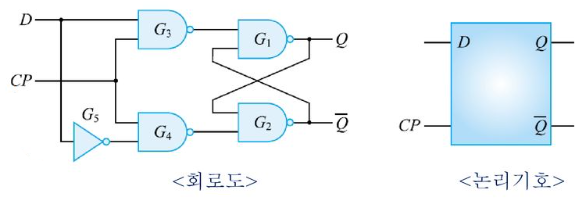

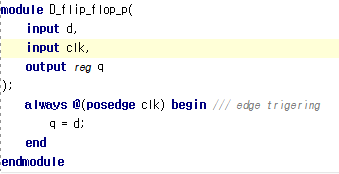

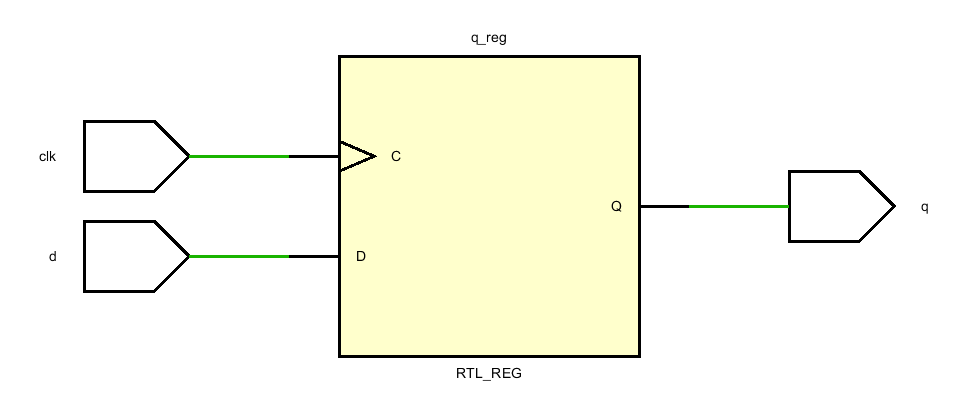

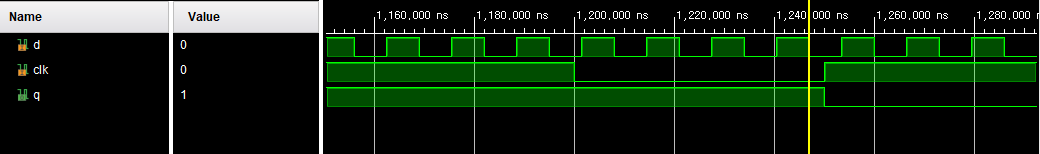

<D Flip-Flop>

Register 중 가장 많이 사용되며 대부분의 순차논리회로가 DFF를 포함한다.

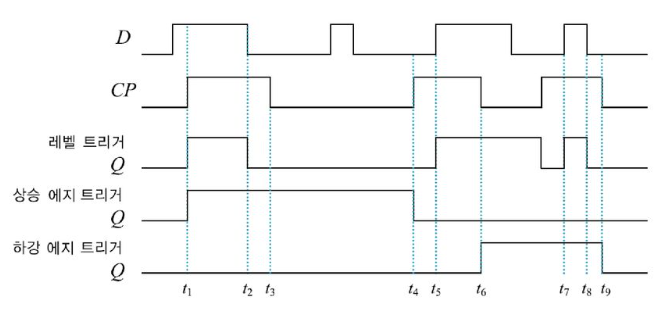

Edge triggered 방식을 사용하며, triggered되지 않는다면, 상태를 기억한다.(Qc = Qn)

DFF를 만드려면, edge detector가 필요한데, glitch가 발생하기 때문에 프로그램이 자체적으로 버퍼를 달아 glitch를 없애버린다.

→ 디텍터는 glitch를 이용하여 edge를 검출해내는데, 버퍼달아서 없어지면 검출 불가

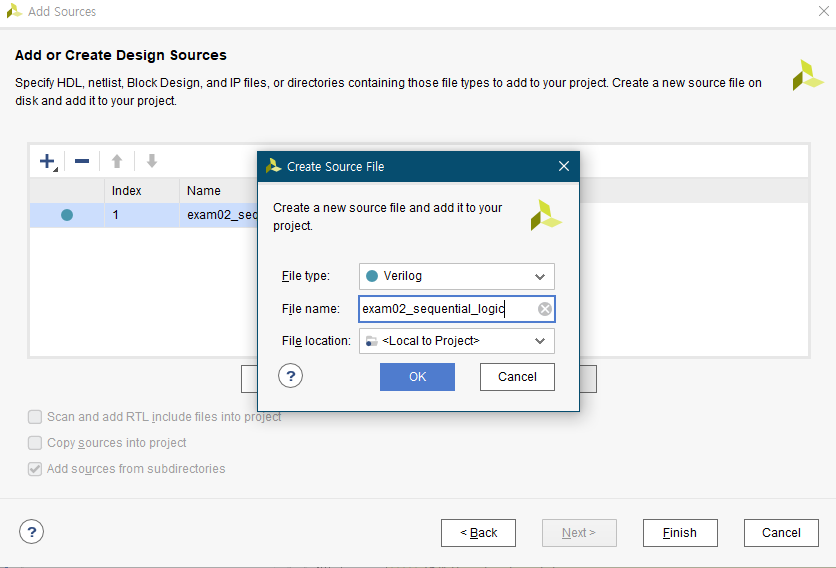

<D Flip-Flop 만들어 보기>

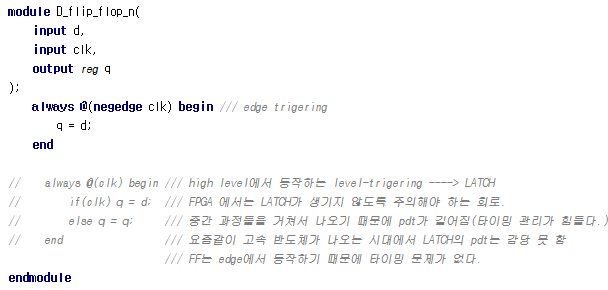

※ FPGA에서는 Latch를 사용하면 안 된다.

왜 와이?

FF와 달리, 중간 과정을 거쳐서 나오기 때문에 pdt 발생(타이밍 관리가 힘들다)

요즘같이 고속 반도체를 설계하는 시대에 Latch의 pdt는 감당 안 됨.

FF는 edge에서 동작하기 때문에 타이밍 문제없음.

∴ Latch가 생성되지 않도록 주의해서 코딩할 것.

예시)

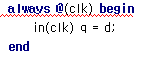

vivado는 이 문장을 보고 LATCH를 만들어 버림

clk의 변화가 생기면 동작하는 건데,

if (clk) 때문에 clk가 0이면 q값을 유지시킨다 ---> LATCH

그러므로 조합논리회로를 always를 이용해서 만들지 않도록 하자. LATCH가 생성된다.

그래도 써야 된다면, if문을 쓴다면 반드시 else만들어주고,

case쓴다면 경우의수를 다 쓰거나 default를 꼭 써주던가 해야 된다.

골치아프니까 그냥 쓰지 말 것.

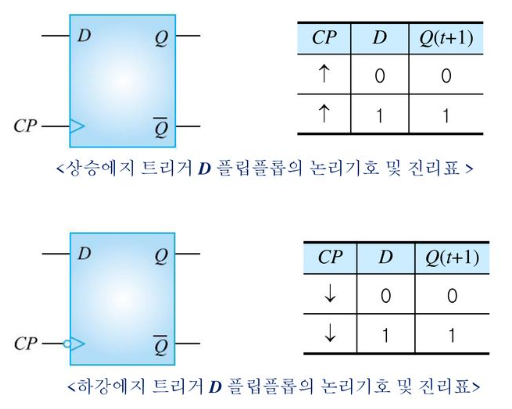

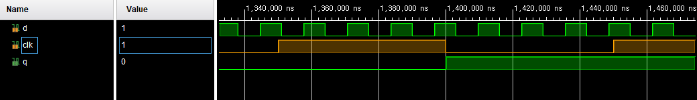

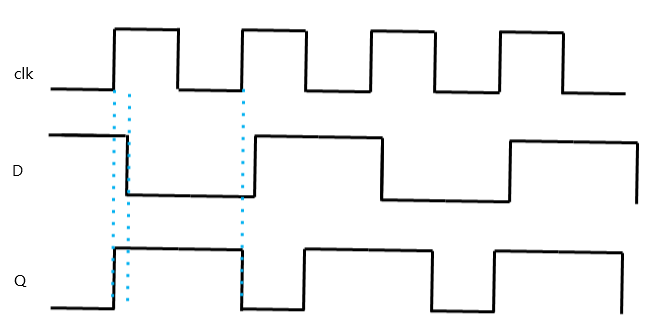

Edge-triggered

Rising edge : 0→1 (posedge)

Falling edge : 1→0 (negedge)

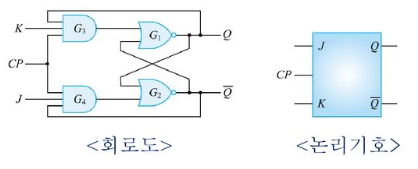

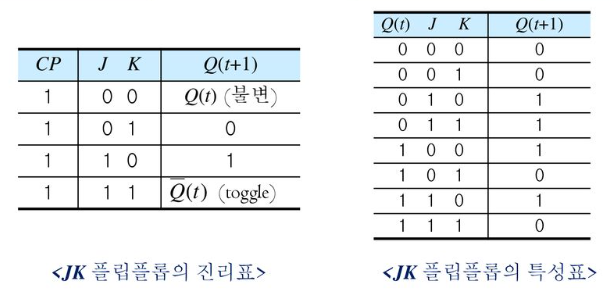

<JK Flip-Flop>

얘는 00, 11 의 입력이 들어간다.

LATCH에서는 위 두 가지가 들어가면 부정출력이 발생한다 했는데,

문제가 없는지 체크해보자.

Q=0, Q'=1, K=J=1이면,

Q : 0 → 0 → 1

Q' : 1 → 0 → 0

결국 1 0 으로 바뀌니까 문제없다.

Q=1, Q'=0, K=J=1이면,

Q : 1 → 0 → 0

Q' : 0 → 0 → 1

0 1 로 바뀌니까 문제없다.

∴ 부정출력은 발생하지 않고 Toggle 동작을 한다.

K=J=0 : hold , K=J=1 : toggle

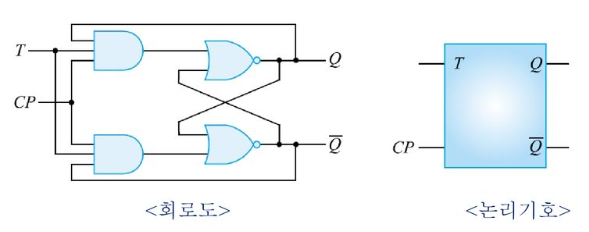

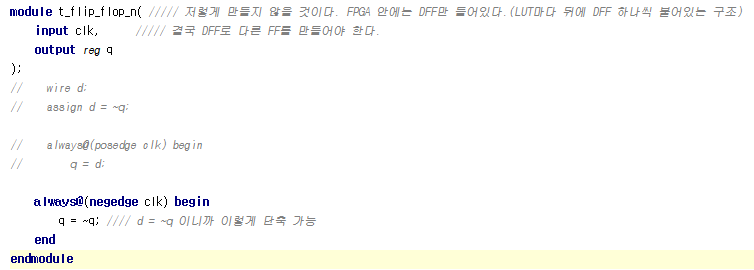

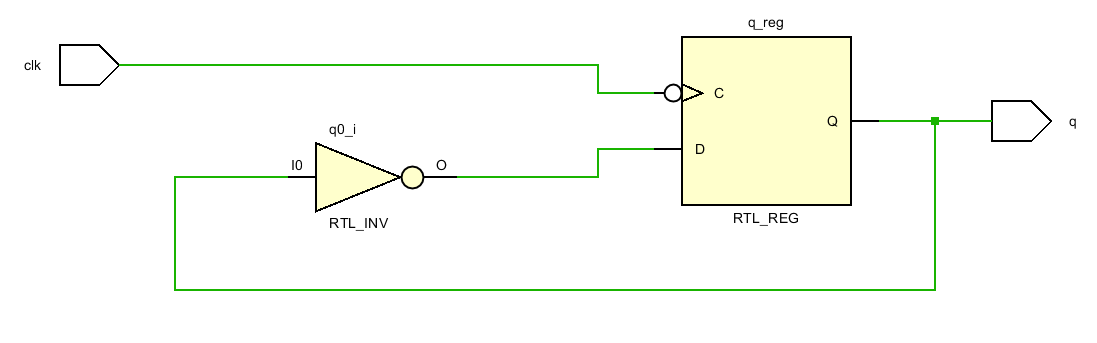

<T Flip-Flop>

JK FF의 입력을 T로 묶어버림.

→ Toggle의 목적으로 만들었다.

※모든 FF는 DFF를 활용하여 만들어야 한다.

FPGA에는 DFF만 존재함.

Gate-level로 모델링해서 만들 수도 있겠지만, 회로도 복잡해지고 게이트도 많이 사용됨.

모든 반도체 소자는 커패시터의 성질을 가지기 때문에 PDT가 존재할 수 밖에 없다.

그러므로 회로를 설계할 때, PDT를 고려하여 여유롭게 출력될 수 있도록 조정해줄 필요가 있다.

'# Semiconductor > [Semicon Academy]' 카테고리의 다른 글

| [Harman 세미콘 아카데미] 8일차 - review, async/sync counter (0) | 2023.06.28 |

|---|---|

| [Harman 세미콘 아카데미] 6~7일차 - 취업 특강 (0) | 2023.06.26 |

| [Harman 세미콘 아카데미] 5일차 - Demux, 코드변환기 (0) | 2023.06.23 |

| [Harman 세미콘 아카데미] 4일차 - Encoder 설계, MUX, LUT (0) | 2023.06.22 |

| [Harman 세미콘 아카데미] 4일차 - 7_segment로 디코더 회로 출력하기 (0) | 2023.06.22 |