[Review]

초반 2시간은 이제까지 했던 것들을 복습하는 시간을 가졌다.

[async / sync]

1. 비동기식(async)

: 요청과 결과가 동시에 일어지 않는 방식

→ 요청을 보낸 후, 응답을 받지 않아도 진행할 수 있다.

→ 즉, FF들이 서로 다른 clk를 사용

▶특징 : 결과를 기다리지 않고 각각 작업 수행 가능

설계가 복잡하고 타이밍 제어(PDT제어)가 잘 안 됨.

∴ FPGA에서는 async를 사용하지 않는다.

2. 동기식(sync)

: 요청과 결과가 동시에 일어나는 방식

→ 요청을 보낸 후, 응답을 받아야 진행된다.

→ 즉, FF들이 같은 clk를 사용

▶특징 : 설계가 간단하고 직관적

요청에 대한 결과가 반환될 때까지 대기해야됨.

[Reset]

FF에서 초기값을 지정해주지 않으면, Z(High Impedance)가 출력된다.

(default 초기값은 z)

위 코드처럼 따로 초기값을 지정해줘도 되지만,

가장 보편적으로 사용되는 방법은 input에 reset을 하나 만들어서 sensitivity list에 넣어주는 방법이다.

① rst = active high(1일 때, rst 동작)

② rstn = active low(0일 때, rstn 동작

reset 변수명은 편한대로 지정하여 사용하면 된다.

① async_reset : 다른 요소에 상관없이 리셋 신호에 의해서만 동작

ex) 버튼을 눌러서 리셋시키는 경우

② sync_reset : clk 펄스의 상승 또는 하강 엣지에 맞춰서 리셋

※ 리셋은 async_rstn을 가장 많이 사용한다.

보통 칩에서 리셋하는 애들은 핀에 풀업 레지스터가 달려 있는데, 가만히 냅두면 1의 값을 가진다.

∴ 리셋 시, 0을 인가하는 것이 안전하다.

[async_counter]

이전 FF의 출력이 다음 FF의 입력으로 들어가는 방식으로, 리플 카운터(Ripple counter)라고도 부른다.

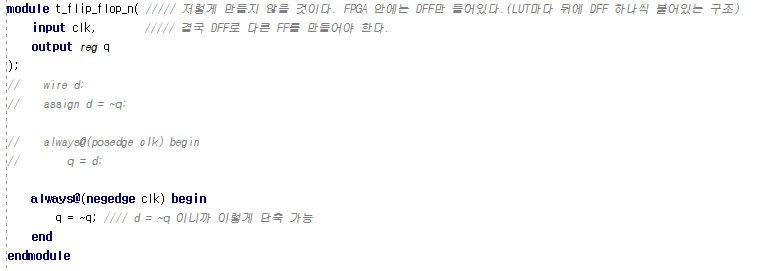

1. up_counter_async

: TFF를 활용하여 만들어지며, 각 FF는 clk의 negedge에서 변화하므로 count가 상승한다.

2. down_counter_async

※ FPGA 에서는 비동기(async)를 사용하지 않는다.

Ex) up_counter_async

1 0 1 0

↓ ↓ ↓ ↓ ------ [1] 에서 negedge가 발생함.

0 0 0 0

↓ ↓ ↓ ↓ ------ [2] 에서 토글이 발생한다.

0 1 0 0

∴ 출력도 바뀌고, 타이밍도 꼬이므로 비동기는 사용하지 않는다.

[sync_counter]

1. up_counter_sync

모든 하위 bit가 1이 되었을 때, 다음 bit를 토글한다.

즉, 하위 bit의 출력을 다 AND로 묶어서 다음 입력으로 사용한다.

2. down_counter_sync

3. up_down_counter_sync

<FPGA board로 출력>

1) Down_count

2) Up_count

3) Reset

4. 동기식 BCD up_counter

5. 동기식 BCD up_down_counter

1) Down_count

2) Up_count

6. Ring counter

※ 다이나믹 구동

: com 단자에 1을 빠르게 주면, 4개 다 켜져 있는 것으로 보인다.

cf) 잔상효과 : 1ms 마다 led를 키면, 다 켜진 것으로 보인다.

- 장점

: data port를 공통으로 써서 port를 절약할 수 있다.

→ 동시에 키려면, 같은 값이 출력되어야 한다.

각 CT별로 다른 값을 출력하기 위해 다이나믹 구동 사용

temp 없이 com으로만 만들어줘도 무관하다.

7. Ring counter를 활용하여 up_down_counter 출력하기

<숲에서 나무로 분석해나가면 좀 편하다.>

① up_down_counter_12bit : 숫자 카운팅(0123456789abcdef)

② ring_count_fnd로 짧은 주기로 LED 하나씩 순차적 점멸시킴(잔상효과로 다 켜진걸로 보임)

③ {4'b0000,카운팅한 값[11:0]}를 4개로 쪼개서 com의 각 bit에 해당하는 hex_value[3:0]에 배정

---> 나름 encoding

④ decoder_7seg로 com의 각 자리에 해당하는 값을 디코딩하여 seg_7로 출력

(0000_0000_0000_0011이 LED 상에 3으로 출력)

※ FND_4digit_cntr는 ②③④를 묶은 Top_module

직사각형 : 다중비트레지스터

정사각형 : 단일비트레지스터

회로 수준에서 레지스터는 모든 클록 트리거 입력이 시스템 클록에 연결된 D형 플립플롭의 배열

원 : 이상적인 조합 논리 회로 연산자

(AND, OR같은 부울연산, 덧셈, 뺄셈과 같은 수학적 연산, 버스에서 비트를 추출하거나 신호를 더 큰 버스로 결합하는 연결 연산 및 조합 회로의 다른 유형의 동작 수행)

사다리꼴은 멀티플렉서, MUX

모든수의 입력을 수용할 수 있으며, 하나의 특정 입력 신호를 선택하여 MUX 출력으로 전달

슬슬 꼬이기 시작

'# Semiconductor > [Semicon Academy]' 카테고리의 다른 글

| [Harman 세미콘 아카데미] 10일차 - Register, Memory (0) | 2023.06.30 |

|---|---|

| [Harman 세미콘 아카데미] 9일차 - Counter 활용(parameter, bin_to_dec, TFF, edge_detector, debouncing) (0) | 2023.06.29 |

| [Harman 세미콘 아카데미] 6~7일차 - 취업 특강 (0) | 2023.06.26 |

| [Harman 세미콘 아카데미] 5일차 - Sequential Logic(LATCH, FF) (0) | 2023.06.23 |

| [Harman 세미콘 아카데미] 5일차 - Demux, 코드변환기 (0) | 2023.06.23 |