[4NAND]

보통 반도체 소자 Design Test에서는 한 소자 당 2시간을 주고 그려보라 한다.

한 번 만들어보자.

📌 Schematic

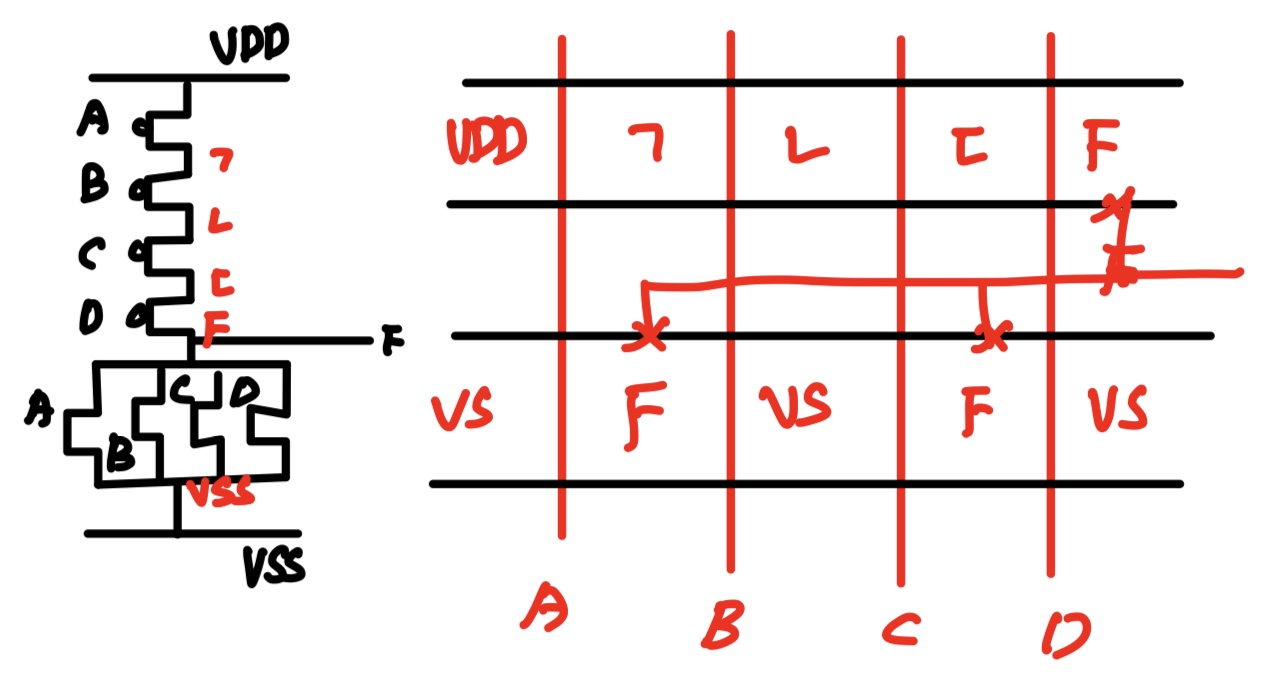

NAND은 pMOS 병렬, nMOS 직렬이므로 위와 같이 Schematic 생성

Symbol도 만들어준다.

📌 Simulation

출력이 변화하는 부분만 짤라서 시뮬레이션 돌리면 됨.

4NAND_TEST file을 생성하여 위와 같이 그려준다.

입력값도 위 진리표처럼

VINA = 1

VINB = 1

VINC = 1

VIND = VIND (얘를 변수로 놓고 시뮬레이션할 것이다.)

pMOS의 적절한 WIDTH는 약 2.14um이므로 2.14um 채택

📌 Layout

5.69um짜리 4NAND gate Layout

DRC와 LVS도 완료

[4NOR]

📌 Schematic & Symbol

NOR는 pMOS 직렬, nMOS 병렬로 배치해야 한다.

📌 Simulation

pMOS WIDTH = 5.96um 채택

📌 Layout

9.51um짜리 4NOR gate Layout 생성

DRC와 LVS도 완료

[MUX]

📌 MUX 개요

[Harman 세미콘 아카데미] 4일차 - Encoder 설계, MUX, LUT

[Encoder] schematic을 생성하면, ROM을 포함하여 생성된다. (4-bit이므로 ROM 내부에 16개의 메모리가 생성됨) 우리가 정해준 4개 빼고 나머지 12개에는 다 2’b11(조건연산자의 가장 마지막 값)을 저장해버

rangvest.tistory.com

MUX를 AND로 구성하면 위와 같다.

AND 게이트는 NOT + NAND로 만들어졌기 때문에,

Tr의 갯수가 6개이다.

총 Tr은 20개이며, 성능을 높여주기 위해 갯수를 줄여보자.

어짜피 두 번 반전되므로 NOT gate를 뺴줘도 같은 값을 출력할 수 있다.

따라서 NAND만으로도 구현할 수도 있으며 Tr의 갯수는 총 14개

트랜스미션 게이트는 일종의 스위치 역할을 하고,

pMOS나 nMOS 측 둘 중에 하나만 입력이 들어와도 On되는 특성이 있다.

위와 같이 트랜스미션 게이트로 MUX를 만들면, 총 6개의 Tr만 사용할 수 있다.

📌 Schemetic & Symbol

일단은 먼저 NAND gate로 구성된 MUX를 만들어 보자.

📌 Simulation

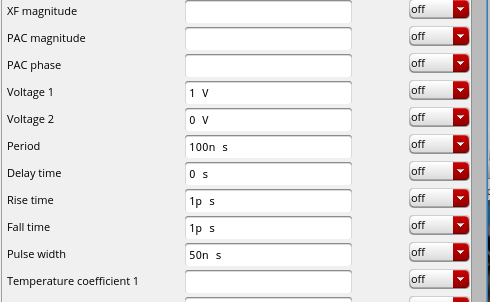

rise time, fall time : 실제로는 상승과 하강하는데 시간이 소요되므로 이 것까지 적용시켜준다. 일종의 딜레이

Pluse Width : Duty cycle이라 생각하면 됨. 10n 주기에서 5n를 줬으니 50% duty

S0의 주기는 VINB보다 크게 주면 된다.

시간을 기반으로 시뮬레이션할 것이므로, Transient로 설정하고 1us동안 돌린다.

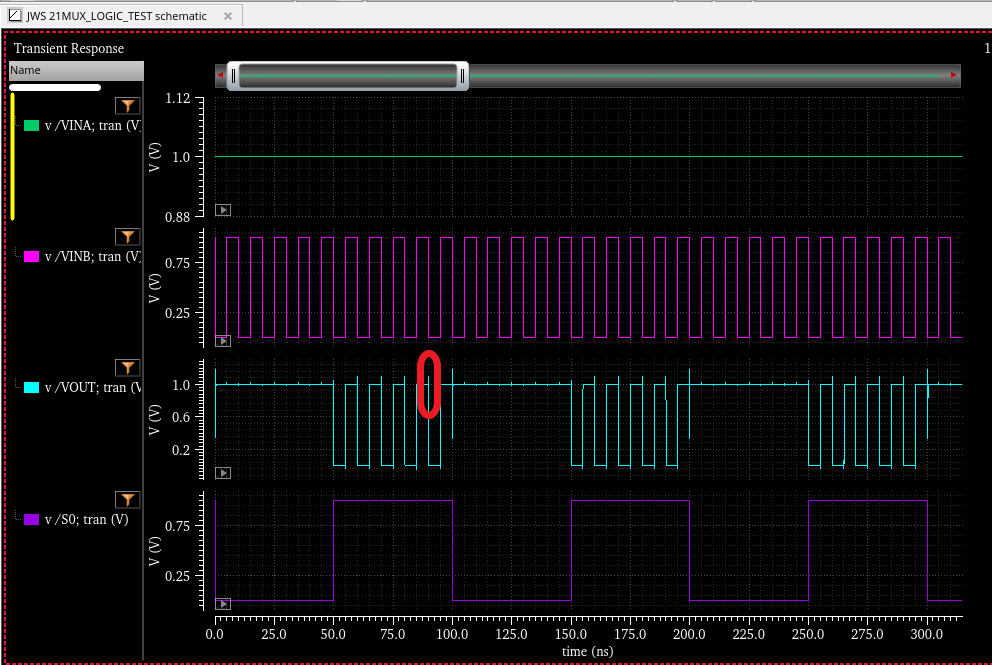

처음에는 이렇게 그래프가 출력될 것이다.

아래처럼 깔끔하고 보기 좋게 정리된다.

위와 같이 튀는 부분이 발생할텐데,

아까 우리가 Rise time, Fall time을 설정해줘서 이렇게 시뮬레이션됨.

📌 Layout

이전에 만들어서 저장한 Layout은 인스턴스하면 그룹으로 묶여있을 것이다.

공통 단자 사용 등, 좀 더 효율적으로 사용하기 위해 쪼개자.

단, Cell로 제공해주는 것은 쪼개면 안 된다.

예를들어 Tr을 쪼갠다면, 더이상 Tr로 인식하지 않는다.

2NAND는 3개이므로 그룹 해제하고 3개 만들어준다.

일단 입출력 라벨 싹 지우고

VDD와 VSS는 공용으로 사용하므로 하나에 연결해버려도 되고,

NAND는 양 쪽의 p+ diffusion을 VDD에 연결하기 때문에 공통 단자로 써도 문제가 없다.

하지만 VSS는 한 쪽의 n+ diffusion에만 연결되기 때문에 공통으로 쓸 수는 없고 최대한 붙여주자.

NOT gate의 pMOS는 유난히 길다.

이럴 때는 Finger를 2개로 분할하여 gate를 하나로 묶어주면

같은 크기지만 공간 효율을 더 좋게 만들 수 있다.

저번 게시글에서 다뤘던 점프선 만드는 단축키를

MUX부터 본격적으로 사용할 것이다.

점프선 : 원하는 메탈 선택하고, 단축키 P + 마우스 우클릭

<Layout tip>

DRC는 다 만들고 돌리지 말고, 중간중간 돌려가면서 확인하면서 작업할 것.

nMOS 기준, 가로 길이가 4.63um

전체 높이는 5.87um인 MUX의 Layout

가장 주의해야할 부분은

S0와 S0'이 연결되는 부분이다.

위 그림에서와 같이 S0'는 Metal1을 점프하여 연결되어 있다.

Schematic을 보면서 차근차근 하면 크게 헷갈리지는 않겠지만,

회로가 복잡해지고 어려워질수록 실수하기 쉬운 부분이다.

cf) gpdk090 Design rule

Poly - Poly >= 0.12um

Metal - Metal >= 0.12um

Poly - Oxide >= 0.1um

Oxide - Oxide >= 0.15um

Pimp - Pimp >= 0.24um

일단 지금은 이 것만 알아둬도 레이아웃 최소화를 좀 더 수월하게 할 수 있을 것이다.