[Stick Diagram]

📌 Stick Diagram

: Layout을 간단하게 막대로 그린 상태도

📌 Design Sequence

1. CMOS Schematioc

2. Simulation

3. Layout(Stick Diagram 그려보고 Tool로 진행)

4. DRC

5. LVS

3~5번까지 수행 가능하면, 레이아웃 엔지니어 가능

📌 Path(경로) 조건

가능한 경로로 선정되기 위해서는 2가지 조건을 만족시켜야 한다.

1. nMOS Block & pMOS Block은 동시에 만족해야 한다.

2. 모든 트랜지스터를 한 번씩 경유해야 한다.

📌 "좋은" 반도체의 기준

좋은 반도체란,

1. Fast : 성능이 뛰어나 데이터 전송 속도가 빠른 반도체

2. Cheap : 가격이 저렴한 반도체

3. Low Power : 전력을 적게 잡아먹는 반도체

위와 같이 3가지 기준 중 하나 이상을 충족시키는 반도체를 의미한다.

Layout의 관점에서 봤을 떄, 우리가 만족시킬 수 있는 조건은 Fast와 Cheap이다.

출력 단자에 Tr을 적게 연결시켜 전송 속도를 빠르게 하거나,

크기를 최소화시켜 가격을 저렴하게 만들 수 있다.

그 중, Fast에 관련된 조건을 살펴보자.

좌측은 NOT gate의 Schematic이고 우측은 Stick Diagram이다.

똑같이 입력을 받아 출력을 내보내는 기능을 하지만,

왼쪽의 막대도는 Tr이 3개 연결되어 3C,

우측의 막대도는 Tr이 2개 연결되어 2C이다.

시정수 τ = R x C 이고, 이때 τ는 딜레이와 같은 역할을 하므로

C값이 클수록 데이터 전송 시간은 길어진다.

따라서 C값이 더 적은 우측의 막대도가 더 "좋은" 반도체 소자이다.

Cost를 줄이는 방법은 또 하나가 더 있다.

바로 공통 단자를 이용하는 것인데,

공통 단자를 활용하면, 면적도 줄고 길이도 감소하기 때문에

비용 절감에 도움이 된다.

위와같이 Layout만으로도 반도체 성능을 충분히 끌어올릴 수 있으니,

Layout Design 시, 한 번 더 생각해보고 작업하도록 하자.

📌 3NAND 예시

여러 가지 Path가 가능하지만, 가능하면 Vout(F)와 연결된 MOS를 가장 우측에 배치하자,

여러 가지 Path가 가능하지만, 그 중에서 더 "좋은" Layout을 선택하는 것이 좋다.

BAC는 3C, ABC는 4C이므로 속도가 빠른 BAC를 채택하는 것이 좋다.

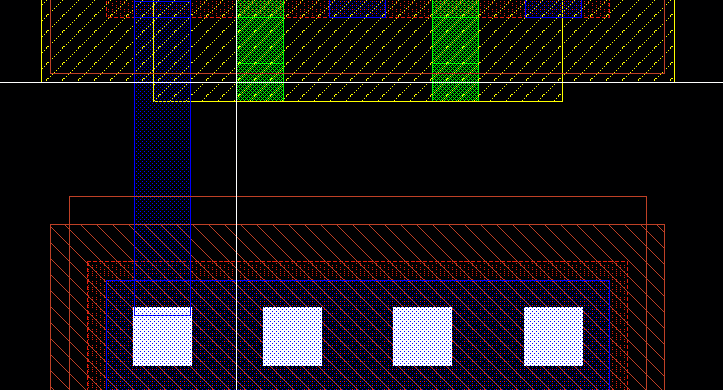

[2NAND Layout]

📌 2NAND Layout 생성

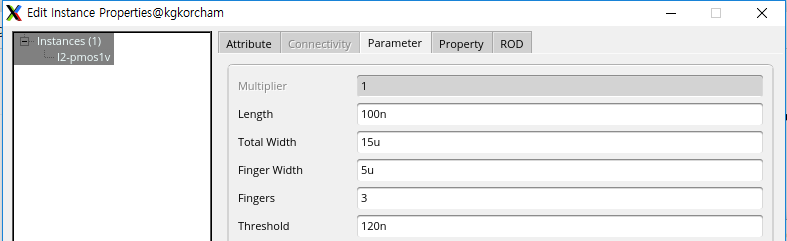

pMOS 하나 nMOS 하나씩 만들어 주자.

Poly 선택하고 단축키 R 눌러서 Poly끼리 연결해주자.

단축키 O 누르고 Group은 Foundray, Via는 M1_PSUB

Stamp Error가 발생하니까 NWELL로 감싸줘야 한다..

.

왼쪽에 있는 것을 점프해서 오른쪽 것만 연결하고싶다면?

단축키 P + 마우스 우클릭

Metal1 Label을 사용해서 라벨을 만들어 주자.

그냥 Metal1을 쓰면 에러 발생하니까, 꼭 확인해주자!

이대로 DRC 돌려보면, 역시나 에러가 발생한다.

간격 셋팅 다시 해주고 DRC 돌려주면,

문제없이 잘 만들어졌다는 메세지가 출력된다.

LVS도 문제없이 통과 완료.

📌 2NAND Layout 최소화

"좋은" 반도체를 만들기 위해, 최대한 작은 사이즈로 만들어주자.

5.6um짜리 2NAND gate Design

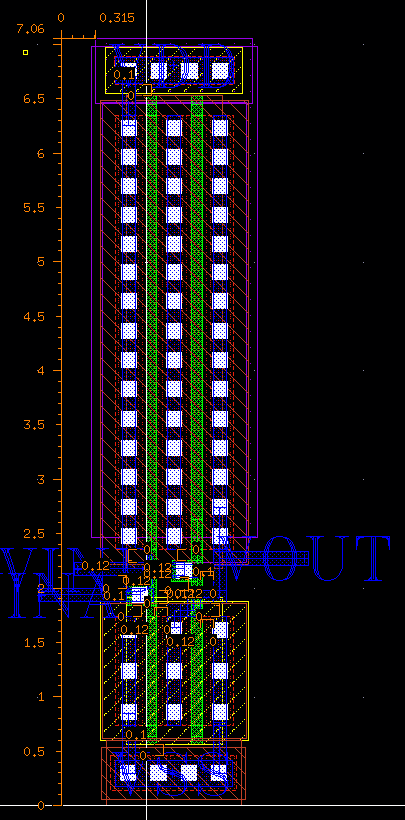

[2NOR Layout]

7.06um로 최소화까지 완료

[3NAND Layout]

📌 3NAND Stick Diagram

병렬로 연결된 MOS는 Source-Drain의 개념을 생각하면 이해하기 쉽다.

VDD는 Source에 연결되어야 하고, F는 Drain에 연결되어야 하므로, VDD F VDD F같은 구조가 된다.

Path를 C-B-A로 배치한 이유는, Vout이 A와 연결되어 있기 때문에 Vout을 우측으로 뺴기 위해서 C-B-A로 설정

VSS는 C와 연결되므로 한 line만 배치

📌 3NAND Layout

5.62um로 최소화한 3NAND gate

[3NOR Layout]

📌 3NOR Stick Diagram

Path는 Vout 기준으로 결정하면 된다.

C와 F가 연결되어 있으므로, A-B-C로 설정

F와 연결된 C쪽에 F를 다 연결시켜서 우측으로 빼고,

한 쪽을 F로 연결했으니 VSS F VSS F로 구성한다.

VDD는 A와 연결되어 있으니 A측에 배치

📌 3NOR Layout

8.31um로 최소화한 3NOR gate