[2NOR]

📌 Schematic

📌 Symbol & Simulation

0.5V 지점에서 변환이 되어야 하므로, 500m

VINB는 0.01 step size로 0~1V Sweep

단축키 M 을 활용하여 마크찍어놓고 보면 편하다.

적절한 W값은 3.99 μ

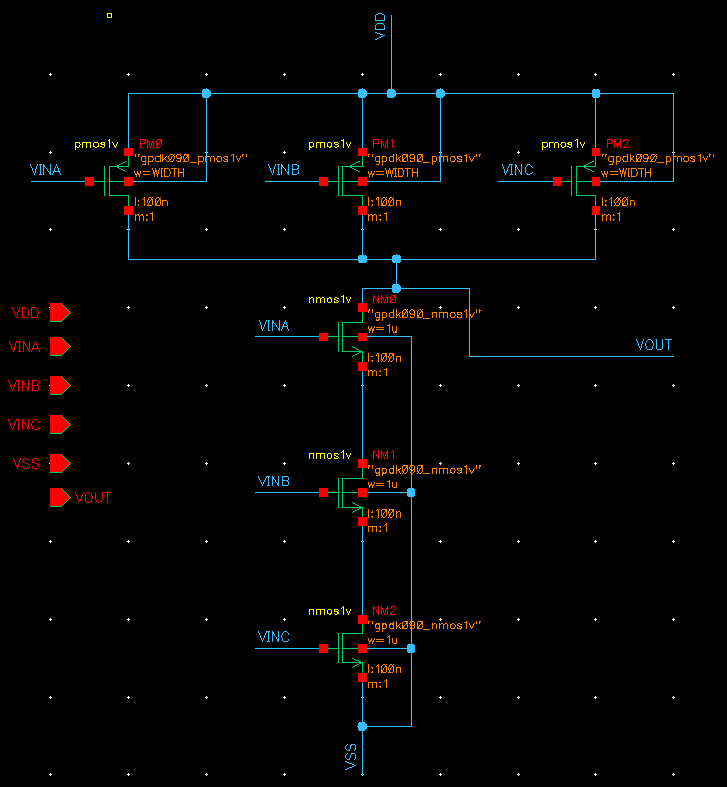

[3NAND]

📌 Schematic

NAND gate는 pMOS 병렬, nMOS 직렬로 구성된다.

📌 Symbol

📌 Simulation

| A | B | C | NAND |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

위와 같이, 출력값이 변환되는 지점이면서

입력 값을 최소한으로 가변하는 구간을 찾아서 시뮬레이션하면 된다.

적절한 W 값은 2.31 μm

[3NOR]

📌 Schematic

📌 Symbol

📌 Simulation

| A | B | C | NOR |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

위와 같이, 출력값이 변환되는 지점이면서

입력 값을 최소한으로 가변하는 구간을 찾아서 시뮬레이션하면 된다.

적정 W의 값은 5.00 μm

[Layout]

📌 Layout 개요

삼전에서 아래 그림을 주고, 위의 그림을 만들도록 한다.

점선을 자른 단면이 위의 그림처럼 나오면 됨.

파란색 빗금 : Net pipe

검은색 빗금 : SiO2

빨간색 빗금 : Polysilicon

아래 그림에서 왼쪽부터 소스, 게이트(빨간 빗금), 드레인, 드레인, 소스

SiO2는 전체적으로 substrate위에 쫙 발려져있고, 검은색 부분은 구멍이라 보면 됨.

그런데 이 그림대로 레이아웃을 만들어서 동작시키면 잘 안 돼

왜 그래?

nMOS의 W/L과 pMOS의 W/L이 같기 때문에

nMOS와 pMOS의 모빌리티는 서로 다르기 떄문에 W/L이 달라야 정상적으로 동작할 수 있다.

제대로 만들 거면, pMOS의 디퓨전을 길게 늘려서 W를 크게 해줘야 한다.

Tap은 왜 존재하는 건가?

핀이 양 방향으로 존재하는 칩은 없다.

한 방향으로만 핀을 위치시키기 위해서 Body를 tab을 통해서 한 방향으로 pin을 배치

📌 Layout 기본 사용법

NOT 아래에 만들어줄 것이다.

Schematic과 좀 다른 창이 출력된다.

Schematic과는 단축키가 다른 것들이 있으므로,

확인하고 사용할 것.

똑같이 그리드 재설정하자

그리드 셋팅을 안 맞추면 Off-Grid 오류가 발생할 수 있기 떄문에

다 똑같이 맞춰야한다. 반드시!

Shift + F Ctrl + F 단축키를 활용하면, 위와 같이 Layer를 On/Off 할 수 있다.

Shift + z Ctrl+ z 단축키를 활용하면,

쉽게 Zoom In / Zoom Out을 할 수 있다.

단축키 K를 사용하면, Ruller 기능을 사용할 수 있다.

원하는 Layer를 선택해서 그리기 위해 단축키 R을 사용한다.

단축키 R을 누르고 클릭~클릭

좌측부터 Nimp / PWdummy / Poly / Oxide_thk / Cont / Metal1

레이어의 크기를 변환하고 싶다면, 단축키 S(Stretch) 기능을 사용하면 된다.

단축키 S 를 누르고 클릭~클릭

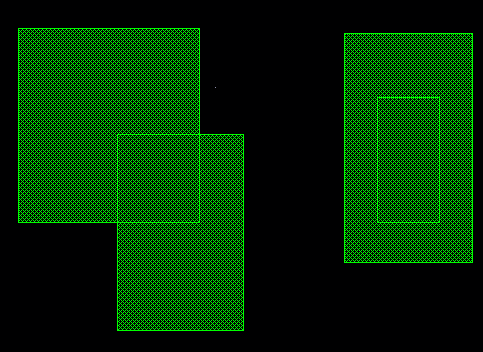

cf) 도형은 가장 바깥 쪽의 변만 고려한다.

좌측 그림의 경우, 사각형이 아닌 팔각형이 되고

우측 그림의 경우, 바깥쪽 사각형(Poly)만 고려된다.

<Layout 기본 단축키 모음>

| 단축키 | 기능 | 설명 |

| M | Move | Layer 위치 이동 |

| C | Copy | Layer 복사 |

| K | Ruller | Layer 측정 |

| S | Stretch | Layer 크기 조정 |

| R | Rectangular Drawing | 마우스로 Layer를 작성 |

| Shift + f | Layer On | Layer 출력 |

| Ctrl + f | Layer Off | Layer 숨김 |

| Shift + z | Zoom In | Zoom In |

| Ctrl + z | Zoom Out | Zoom out |

이제까지 배운 단축키의 기능들을 활용하면

위 그림처럼 레이아웃을 직접 설계할 수 있다.

Q. 왜 이렇게 안 씀?

A. 통으로 뚫어서 쓰는 것(저항이 직렬로 연결됨)보다

3개를 뚫은 것의 저항값이 더 작기 때문에(저항이 병렬로 연결됨)

구멍을 각각 뚫어서 연결한다.

📌 Not gate Layout

전에 만들어 둔 NOT gate의 pMOS의 W = 2.91um이었고

그 값을 적용해주자.

참고) nMOS와 pMOS의 모빌리티는 다르기 때문에 W값이 다르다

Poly는 Poly끼리 연결해준다.

변에 딱 맞추지 말고 겹치는 것이 오류가 없겠지?

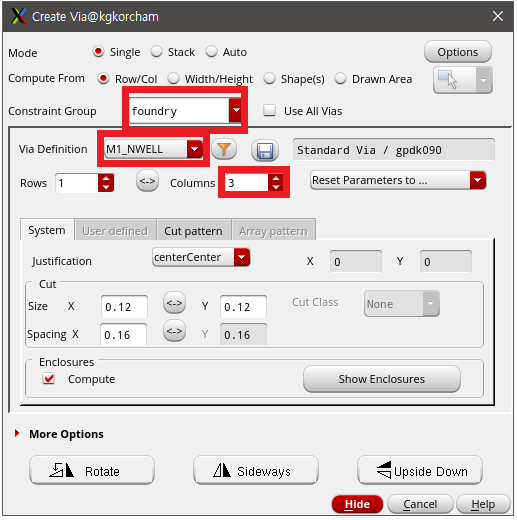

단축키 O를 클릭하여 Creat Via 창을 열어서 Via를 셋팅해줄 수 있다.

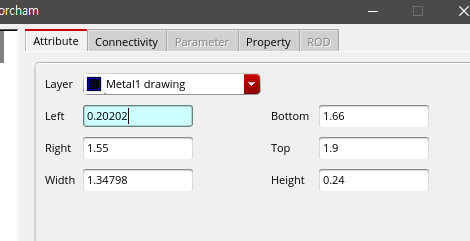

Metal1 Drawing과 Metal1 Label은 육안으로 구분이 불가능하다.

그러니까 Q 눌러서 속성가서 구분하고 사용하도록 할 것.

확인 안 하고 썼다가는 나중에 오류 폭탄맞음.

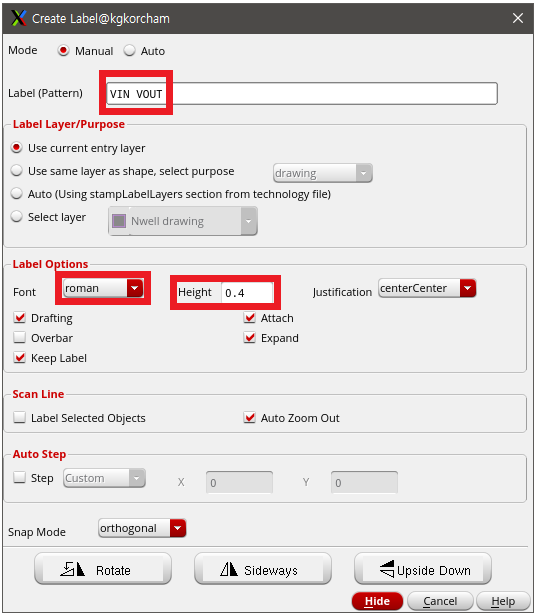

Label을 셋팅할 것인데,

폰트 : roman & 크기 : 0.4 가 가장 적합하다.

Label은 반드시 Label을 붙일 Metal1 내부에 배치되어야 한다.

위 그림과 비교해봤을 때,

검은색 바탕 배경은 P-substrate에 해당하는 부분이라 보면 된다.

P-substrate 위에 pMOS와 nMOS가 배치되어 있고,

Metal1이 배선처럼 각 MOSFET의 단자들을 연결시켜준다.

[DRC & LVS]

예시를 하나 들어보자.

만약 선임이 Chip을 하나 개발하고 Schematic을 만들었다.

그 Chip의 Layout은 내가 맡게 되었고, 만들어진 Layout을 가지고

삼성전자에 제작 의뢰를 맡겼다.

그런데 막상 제작된 Chip은 동작을 하지 않는다.

이 때, 과실 여부를 어떻게 따지게 될까?

① 선임 잘못이라면, Schemetic Error

② 내 잘못이라면, Layout Error

③ 삼성 잘못이라면, 공정 문제

나와 선임은 설계 단계에서는 문제가 없다는 사실을 증명해야 한다.

그 것들 중 Layout 단계에서 증명해야될 것이 바로 DRC와 LVS이다.

DRC는 삼성전자에서 준 Design Rule(파운드리 회사에서 줌)에 맞춰서 작성했는지,

LVS는 Schematic과 Layout이 Match가 되는지 검증하는 과정이다.

해당 문제 발생 시, DRC와 LVS 파일을 증빙자료로 제출하고

위 과정에서 문제가 없다면, 우리 과실은 없음. 삼전 잘못ㅇㅇ

cf) Error 50,000개 vs 다시 그리기

DRC 돌렸어.

근데 Error가 50000개가 발생했어

다시 그려? 아니면 Error 다 잡아?

다 잡아야 됨.

내가 디자인 룰을 모르고 작업했기 때문에 에러가 발생하는 것이다

다시 그려도 결국 에러 발생함

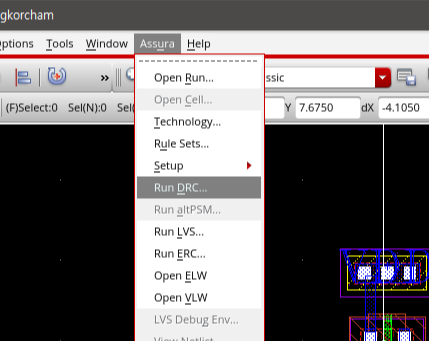

📌 DRC(Design Rule Check)

Assura → Run DRC 클릭

현업에서는 아슈라 대신 캘리버로 쓰여 있을 수 있다.

Run name 작성해주고 Tech는 gpck090 선택

이후에 나오는 안내 메세지는 다 Ok 또는 Yes 누르면 됨.

그러면 위와 같이 발생한 에러가 쭉 출력된다.

1번 Error는 아래에서 다룰 예정

4~5번은 각 Metal1 Layer 사이의 최소 거리를 지키지 않아서 발생하는 오류로 이 것도 아래에서 다룰 예정

2~3번 Error를 보면, Float이면서 최소 거리가 지켜지지 않았다고 되어 있다.

Well을 1.2u만큼 띄우던지, 아니면 하나로 다 싸버리던지 하면 된다.

Layout은 Grid 즉, 격자 기반으로 작성되기 때문에

소수점 셋째 자리를 넘어가는 등, 격자에 해당되지 않는 좌표에 그려진다면,

Offgrid Error가 발생하게 된다.

"나중가면 이 메세지가 아주 반가워질 것이다."

by Choi

📌 LVS(Layer vs Schematic)

위와 같이 Match 라는 메세지가 출력되면 성공

만약 다른 점이 있어서 Match가 되지 않는다면, 어떻게 수정할까?

LVS Report이며, Mismatch가 발생했다는 내용이 담겨져 있다.

Ok 눌러서 넘어가자

에러 part를 더블클릭하면, Schematic창이 추가로 하나 뜨는데,

여기서 Probe 버튼을 누르면 Match가 되지 않는 부분을 Highlight해서 알려준다.

📌 최적화

이렇게 열심히 22명이 레이아웃을 만들었는데, 과연 다 채택해서 쓸까?

그렇지 않음.

만약 여러 개의 레이아웃이 있다면,

동일한 조건에서 가장 작게 레이아웃된 것을 사용한다.

반도체는 같은 성능을 낸다면, 크기가 가장 작은 것을 채택한다.

가장 작게 만들어보면, 5.84um까지 줄일 수가 있고, DRC & LVS 결과 이상없이 잘 만들어졌다.