[SWITCH]

2x1 MUX를 만들 때, Tr 갯수를 최소화시킬 수 있는 방법은

SWITCH를 쓰는 것이다.

SWITCH를 한 번 만들어 보자.

📌 Schematic

심볼은 안 만들 거니까 최대한 깔끔하고 컴팩트하게 만들어보자.

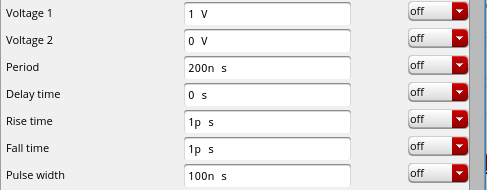

pMOS와 nMOS가 각각 1개일 때의 WIDTH는 2.91u로 이미 알고 있다(NOT gate에서 검출했음)

2.91um로 쓰자.

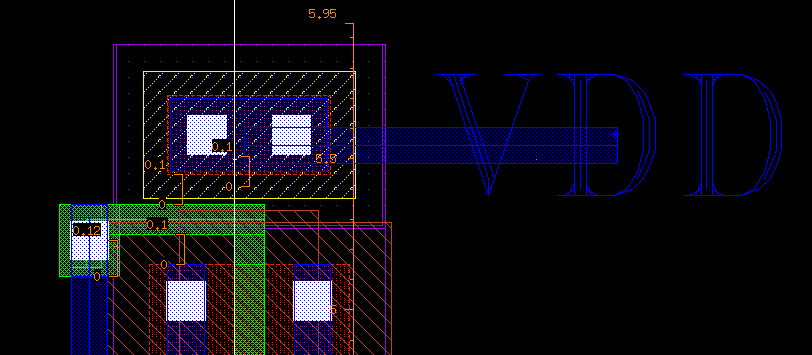

📌 Layout

이번에는 막대도를 그리지 않고 Schematic만 보고 그릴 것이다.

앞으로도 막대도 없이 Schematic만 보고 그리는 습관을 들이는 것이 좋다.

(회로가 복잡해지면, 막대도도 만들기 힘들어)

주의해야할 점은 VDD와 VSS의 연결이다.

이전까지는 Diffution에 VDD와 VSS가 연결되었지만,

이번에는 Body와 연결된다.

따라서 VDD와 pMOS는 NWELL로

VSS와 nMOS는 PWdummy로 감싸주면 된다.

(pMOS의 body : N+)

(nMOS의 body : P+)

최소화까지는 아니고, 일단 적당히 5.88um짜리로 Layout 생성

[2x1 MUX를 SWITCH로 구현]

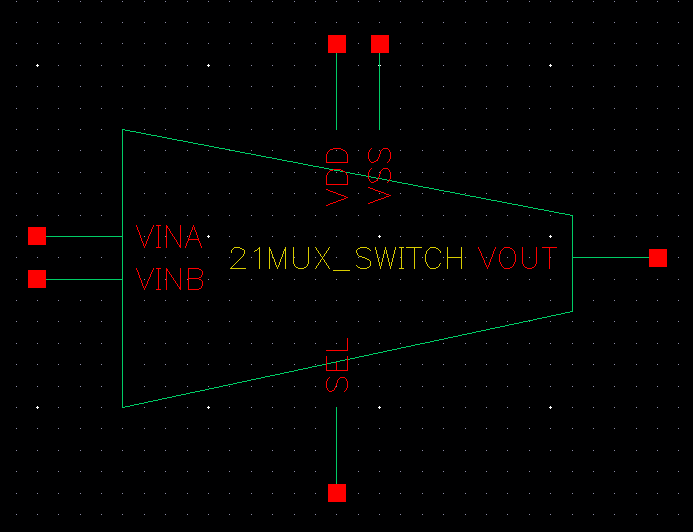

📌 Schematic & Simbol

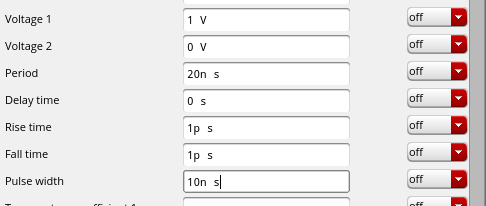

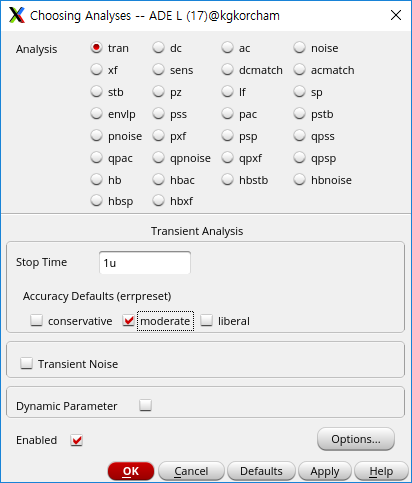

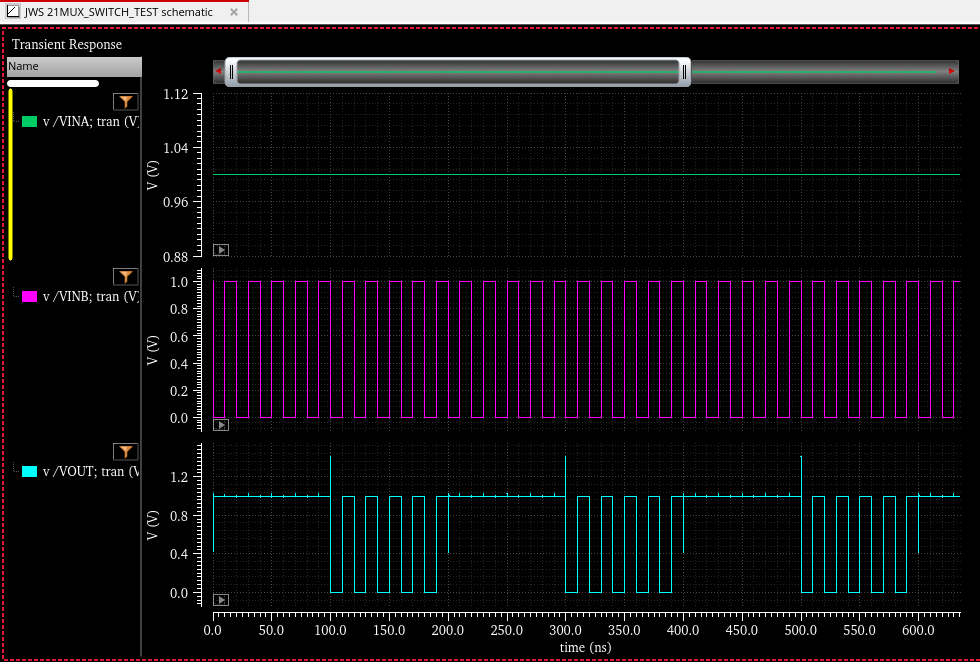

📌 Simulation

2x1 MUX_LOGIC 시뮬레이션 하듯이 하면 된다.

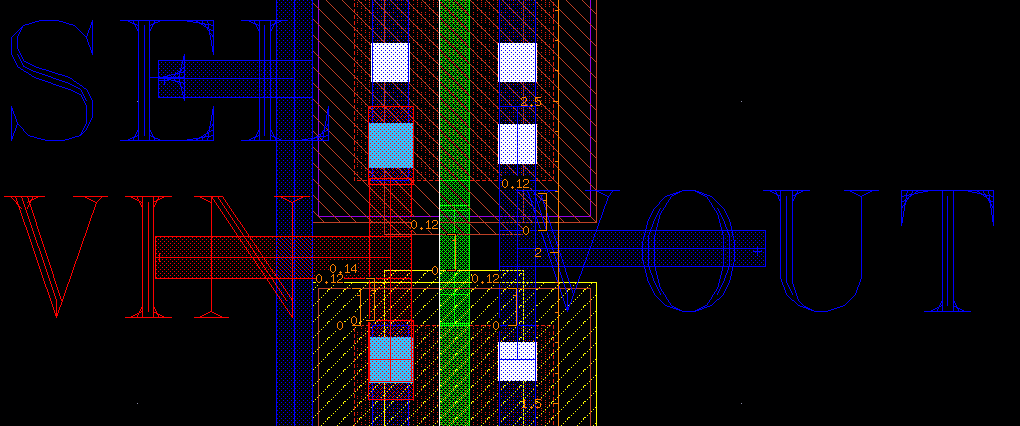

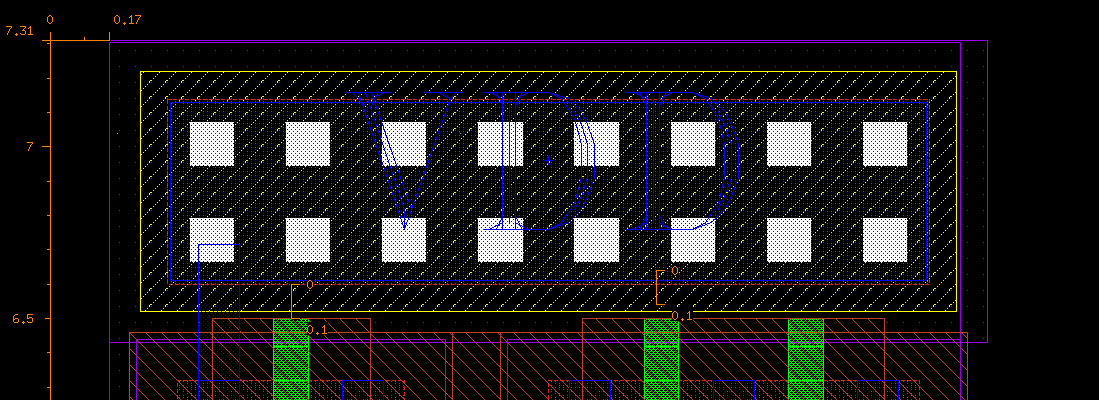

📌 Layout

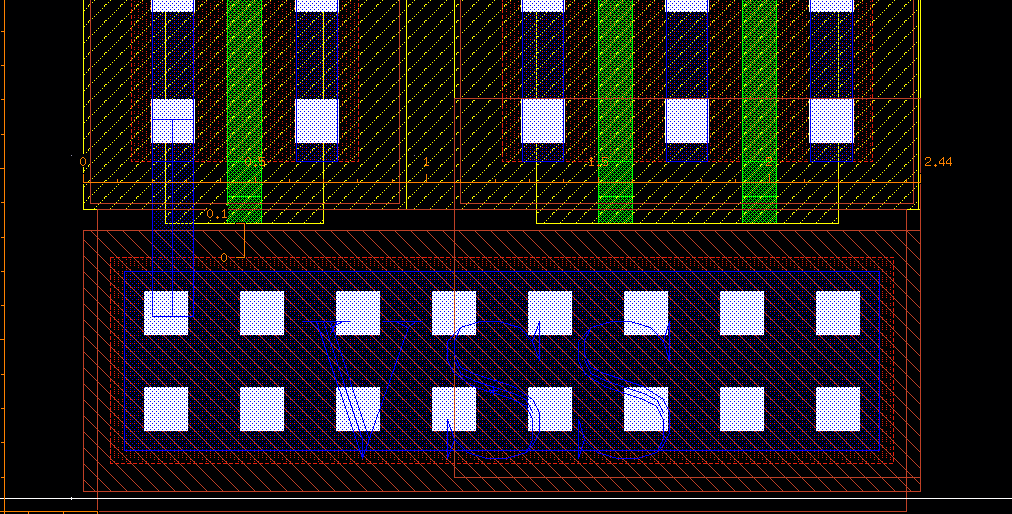

가로 2.44um(nMOS기준), 세로 7.31um 짜리 2x1MUX_SWITCH Layout 생성

✅ 주의 사항

1. pMOS는 Pimp, nMOS는 Nimp로 감싸주지 않으면, 서로 다른 영역으로 인식해서 DRC Error 발생

2. 위 레이아웃에서는 이미 최소화된 상태라 VDD VSS와 MOS의 Body가 붙어 있는데,

만약 떨어져 있는 경우에는 Body를 꼭 연결시켜줘야 한다.

- pMOS는 NWELL

- nMOS는 PWdummy

✅ Tip)

1. 소자를 계속 쓰다보면, Metal에서 메탈라이제이션이 발생하여 단선되는 경우가 종종 있다.

따라서 레이아웃 시, 칩 안에서 가용 가능한 면적이 허용되면 두껍게 해주면 좋다.

-> 위 레이아웃을 보면, VDD와 VSS를 2 줄로 두껍게 만들어 줬다.

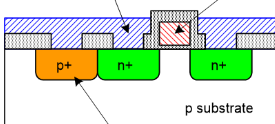

2. 회사마다 제공하는 라이브러리가 다 다르기 때문에, CMOS의 Mask와 pdk를 매칭시킬 수 없다.

예를 들어보자.

상단 그림은 nMOS를 쪼개놓은 것(pdk)이고, 하단의 그림은 nMOS의 Mask이다.

굳이 매칭시켜보자면, Metal과 Metal1, P substrate와 검은색 바탕 이렇게까지는 매치가 되지만,

다른 항목들은 pdk와 Mask의 매칭이 불가능하다.

그러면 어떻게 그려야 돼?

W/L 값만 안다면 어떤 라이브러리를 사용하더라도 레이아웃을 쉽게 작성할 수 있기 떄문에

W/L 값만 시뮬레이션으로 잘 알아내면 된다.