[ATmege128 개요]

마이크로 컨트롤러

CPU, ROM, RAM과 전류 Fanout을 늘린 I/O 확장용 GPIO제어기가 한 침에 함께 구성되어 주로 단순한 반복 작업을 하기 위한 제품에 장착되는 작은 보드 등을 통한 자동화 장치 등에 사용된다.(GPIO : General perform input / output)

- 임베디드 환경에 적합한 저전력 소모의 칩이며, 내보에 32개의 범용 레지스터가 내장됨.

- 유비쿼터스 및 센서 네트워크를 위한 소형 시스템에 적합

- 유사 RISC아키텍쳐(RISC Like architecture)

: 유사 아키텍쳐라고 하는 것은 RISC 구조를 따르고 있으나 명령어와 주소 지정 방식의 수가 RISC에 비해 많기 때문.

1) 스위치, 센서 등의 입력 장치

- 키보드 역할

- 제어 입력 신호를 발생시키는 역할

2) LED, LCD, Motor, Relay 등의 출력장치

- 모니터 역할

- 제어 신호를 이용하여 시스템을 제어하는 역할

특징

- 프로그램을 다운로드하여 저장할 수 있는 2K~128K 바이트의 플래시 메모리 저장

- 내부 EEPROM 용량 : 128~512 바이트까지 가능

- 내부 오실레이터에 의해 동작하는 워치독 타이머와 전 이중방식의 다양한 외부 접속장치 내장

- 다양한 인터럽트 소스와 파워 절약모드 외부 메모리 추가 가능

- 내장 디바이스

: 타이머/카운터, 직렬 통신장치, 아날로그 비교기,

외부 데이터 장치, 인터페이스, 입출력포트,

SPI(Serial Peripheral Interface), 아날로그 디지털 변환기(ADC) 등

8bit AVR의 종류

1) Tiny(ATiny)

: 소형 시스템에 적합아며, 외형 핀 8~20개,

메인 MCU보다 여러 회로를 하나의 소자로 구현한

보조 역할의 칩으로 사용(리모컨)

2) Mega(ATmega)

: 대형이고 입/출력 핀의 수가 많은 시스템에 적합하며,

무선 전화기 및 프린터용 제어기,

FAX 및 CD-ROM 제어기, 통신장비 등에 응용됨.

3) XMEGA(ATxmega)

: 일반적인 목적, 용도는 Mega 시리즈와 같음

4) Automotive AVR

: 자동차와 같은 환경을 위한 환경에 강한 튼튼한 디자인 및 CAN 통신

개인용 컴퓨터와의 차이

- Havard Architecture로 구성되어 있다.

- 프로그램과 데이터가 서로 다른 메모리 영역을 차지하며, 각각의 어드레스, 데이터, 제어 버스가 존재함

- 프로그램 명령과 데이터를 동시에 읽을 수 있으며, 명령어 구조는 RISC(Reduced instruction set computer) 구조를 사용함.

(RISC : 간단한 명령어들의 집합 체계)

폰 노이만 vs 하버드

Von Neumann arcitecture

- 내장 메모리 순차 처리 방식으로 데이터 메모리와 프로그램 메모리가 구분되어 있지 않고

하나의 버스를 가진 구조때문에 CPU가 명령어와 데이터에 동시에 접속 불가

- 메모리 값을 읽고 쓰는 구조이기 때문에 기억장치에 병목 현상이 발생한다.

Havard architecture

- 명령용 버스와 데이터 버스를 물리적으로 분할

- CPU가 명령어와 데이터를 동시에 접근 가능

- 처리 속도를 높이려면, 보다 많은 전기 회로가 필요함.

- 두 개의 버스와 메모리를 가지게 되므로 CPU 코어에서 공간을 많이 차지함.

| 구분 | Von neumann | Havard |

| 목적 | CPU는 한 번에 단일 명령어 실행 가능 | 병렬처리를 위해 메모리 분리 |

| 메모리 | 하나의 메모리 공유 | 명령어, 데이터 메모리 분리 |

| 프로세스 | 메모리 → FI → 메모리 → DI → 메모리 → FI → Store(메모리)와 같이 순차적으로 수행된다. | 명령어 메모리 → FI Store → 데이터 메모리 동시에 명령어와 데이터 처리 가능 |

| 장점 | 공용 메모리 사용으로 상대적 구현 비용이 저렴 | 파이프 라이닝 기술 사용을 위한 환경 제공 |

| 단점 | 파이프 라이닝 기술 사용 시, 메모리 공유 문제 발생(병목현상) | 별도 메모리 사용으로 비용 증가 및 회로구조가 복잡해짐 |

| 적용 사례 | 일반적인 범용 CPU | Microchip Technology의 PIC, Atmel AVR, 현재 범용 CPU(Intel 펜티엄 이후) |

현대의 architecture

: CPU의 외부적으로는 폰 노이만 구조를, 내부적으로는 하버드 구조를 적용하여 속도를 향상시킨 제품도 많다.

기본적으로는 폰 노이만 구조를 기반으로 만들었기 때문에, 병목현상만 일부 해결되었고 메모리속의 프로그램을 순차적으로 실행하는 근본 구조는 변하지 않음.

[ATmega128의 특징]

1) 개선된 RISC구조

- 대부분 단일 클록에서 실행되는 133개의 명령어

- 8비트로 구성된 32개의 범용 작업 레지스터

- 16MHz에서 16MPIS(Milliom Instruction Per Second)

- 2사이클에서 실행되는 내장 곱셈장치

2) 프로그램 메모리와 데이터 메모리

- ISP가 지원되는 128Kbyte의 플래시매모리(10,000번의 쓰기/지우기)

- 부트 코드 영역

- 4Kbyte의 EEPROM

- 4Kbyte의 내부 SRAM

- 소프트웨어에 의한 LOCK동작

3) JTAG(IEEE standard 1149.1과 호환)

- JTAG를 통한 Boundary Scan 방법

- On chip Debug 지원

- JTAG 인터페이스를 통한 Flash, EEPROM, 퓨즈, Lock 비트 설정

4) 내장 입출력 장치

- 별도로 동작하는 프리스케일러와 출력 비교 장치로 구성된 2개의 8bit 타이머/카운터

- 프리스케일러, 출력 비교 장치와 입력 캡처로 구성된 2개의 16bit 타이머/카운터

- 외부 오실레이터에 의한 Real time Counter

- 2개의 8bit PWM 채널

- 2비트에서 16bit까지 조절이 가능한 6개의 PWM채널

- 8채널의 10bit ADC

: 8개의 싱글 입력 / 7개의 자동 입력 / 1x, 10x, 200x, 이득으로 이루어진 2개의 차동 입력

- 바이트 중심의 TWO-Wired Interface(동기 2선식 통신)

- 2개의 UART(Universal Synchronous & Asynchronous Receiver/Transmitter)

- SPI(Serial Peripheral Interface, 동기 3선식 통신)

- 별도의 오실레이터로 이루어진 Watchdog Timer

- Analog Comparator

- 53개의 범용 입출력 포트

5) Power-on Reset

- Brown-out 검출기

- 외부 및 내부 인터럽트 소스

- 6개의 Sleep mode

[ATmega128의 구조]

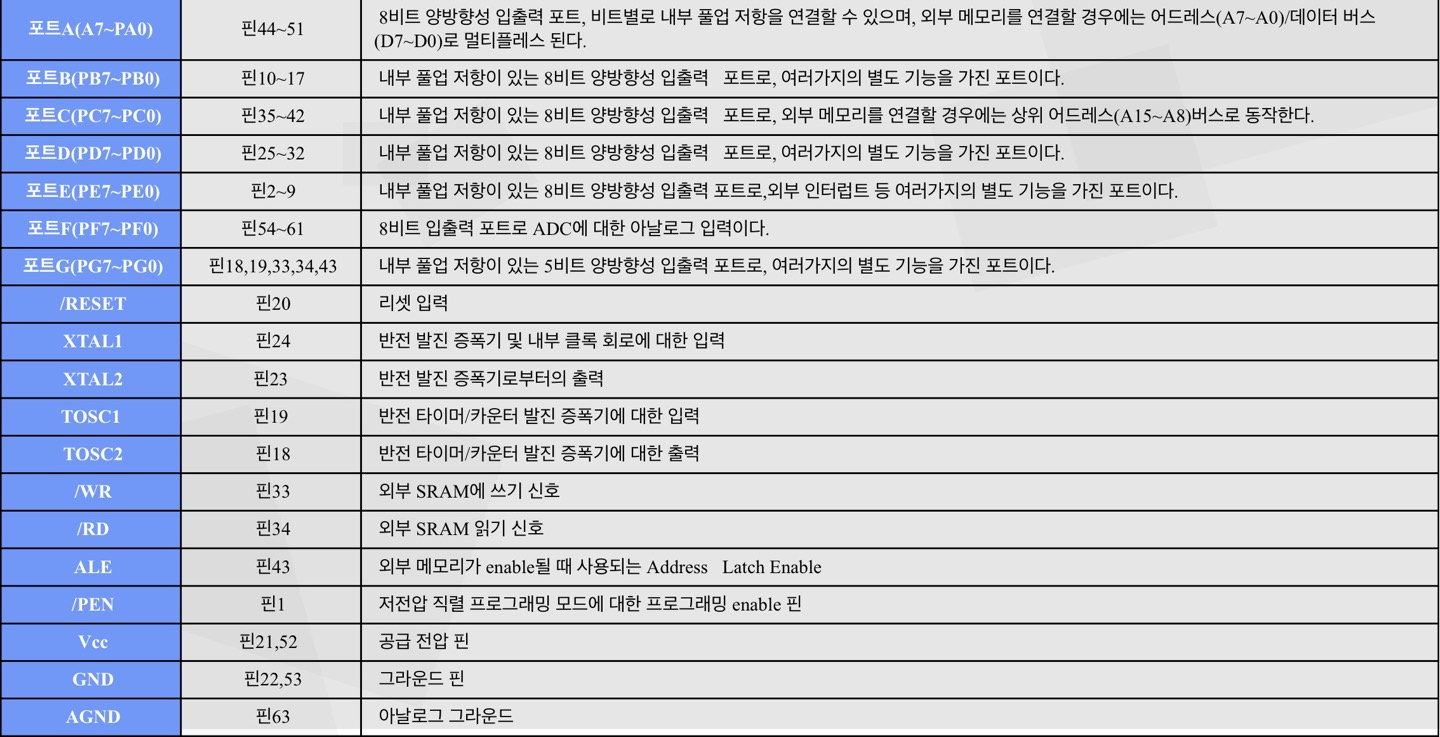

ATmega128의 핀 구조

- 8bit 병렬 입출력이 가능한 7개의 포트(A, B, C, D, E, F, G)

(port G는 5bit)

- 전원(Vcc, GND)

- 클록(XTAL1, XTAL2)

- 리셋(RESET)

- 프로그램 관련(PEN)

- ADC 관련(AVCC, AREF, AGND)

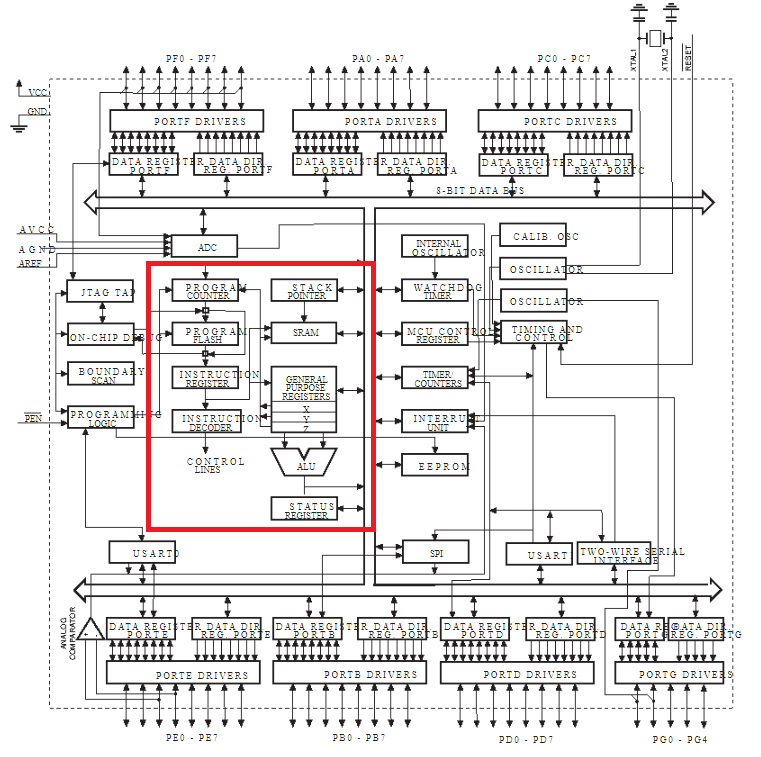

ATmega128의 내부 구조

ALU(Arithmetic Logical Unit)

- 산술 연산기

- 산술연산(+, -, *, /), 논리연산(AND, OR,NOT), 비트연산

1. 상태레지스터(State Register)

ALU가 가장 최근에 실행한 산술연산 명령의 결과에 대한 상태를 표시하는 레지스터

상태 bit는 조건부 처리 명령에 의하여 프로그램의 흐름을 변셩하는데 사용

인터럽트를 실행할 때 PUSH되거나 POP되지 않으므로 사용자가 이를 소프트웨어로 처리해야 한다.

(ex : _delay.ms()함수를 쓰면, 해당 시간동안 CPU 멈춤)

Bit 7 (I : Global Interrupt Enable)

- 전체 인터럽트 허용

- SEI 및 CLI 명령으로 이 비트를 각각 set 또는 reset 가능

- 인터럽트 처리가 시작되면 이 비트는 자동적으로 클리어되며, 나중에 RETI 명령을 만나면 원래 상태 복구

- 각 인터텁트를 개별적으로 허용하는 것은 인터럽트 마스크 레지스터에 의해 결정

Bit 6 (T : Bit copy Storage)

- 비트 복사 명령인 BLD(Bit load) 및 BST(Bit Store) 명령을 사용

- 이 비트를 조작 비트의 출발지 혹은 목적지로 사용

- BST에서는 레지스터의 지정 비트가 T에 들어가고,

BLD에서는 T의 내용이 레지스터의 지정 비트로 들어감.

- 잘 안 씀

BIT 5 (H : Half Carry Flag)

- BCD 연산을 위한 것으로 자리올림(Half-carry)이 발생할 경우 set됨.

- 뺄셈의 경우, 반 빌림수(Half-borrow)가 발생하면 1, 발생 안 하면 0으로 set

BIT 4 (S : Sign Bit = N XOR V)

- 음수를 나타내는 N 플래그와 오버플로우가 발생했음을 알리는 V 플래그의 XOR연산 결과가 1이면 set되고 그렇지 않으면 클리어됨.

- 이 bit는 부호없는 정수 및 부호있는 정수들의 크기를 판단할 때 자주 사용

Bit 3 :(V : Two;s Complement Overflow Flag)

- 2의 보수 연산에서 자리 올림이 발생했음을 알림

- 이 flag는 BRVS와 BRVC 명령에서 분기조건이 이루어지는 기준으로 사용

Bit 2 (N : Negative Flag)

- 산술 연산 및 논리 연산의 결과가 음수일 때 1로 set

(2의 보수 사용 시에 최상의 비트가 1이 되면)

- 연산 결과가 음수라는 것을 표시

Bit 1 (Z : Zero flag)

- 산술 연산 및 논리 연산의 결과가 0이 되면 1로 set

- zero flag는 0이 아닌 1로 set됨(헷갈리지 말 것)

Bit 0 (C : Carry Flag)

- 산술 연산의 가산 및 논리연산의 결과 자리올림(carry)이 발생했음을 알림

- 감산에서 이 비트가 자리 내림(borrow)을 표시

2. 범용 레지스터(General Purpose Resister)

AVR ATmega128은 "Register to Register" 구조로 되어 있으며,

RISC를 실현시킨 CPU이므로 누산기(Accumulator)가 없으며 R0~R31까지 32개의 8bit 범용 레지스터를 가지고 있다.

기본적인 사칙연산을 수행할 수 있으며, 즉시 데이터(immediate data)를 사용하는 일부의 연산명령은 R16~R31에서만 수행

3. X, Y, Z 레지스터(General Purpose Resister)

32개의 범용 레지스터 중에서 R26~R31은 각각 2개씩 합해져서 3개의 15bit 레지스터(X, Y, Z)로 사용 가능하며,

이 16bit 레지스터들은 주로 데이터 메모리의 16bit address를 간접 지정하는 Address pointer로 사용한다.

또한 Z레지스터는 LPM, ELPM, SPM 명령에서 프로그램 메모리 영역의 상수를 액세스하는데 사용하기도 한다.

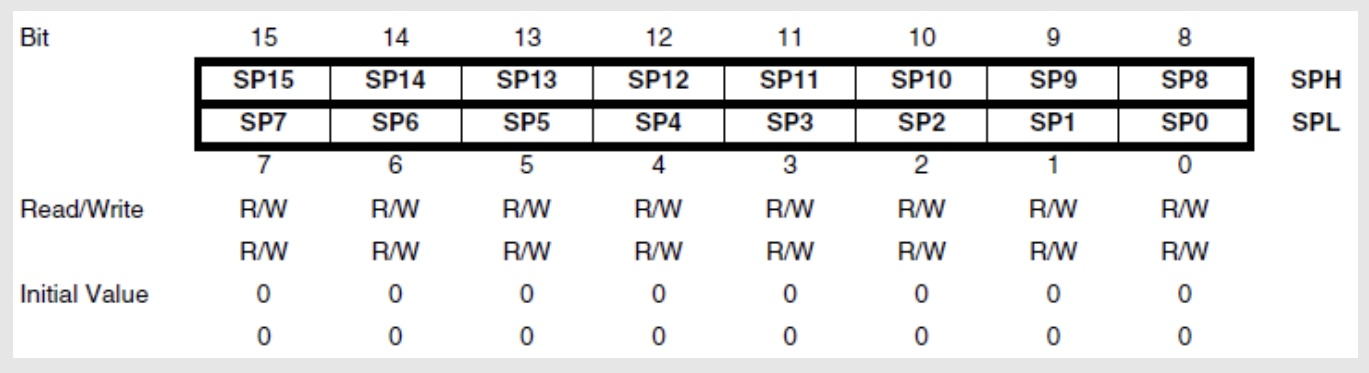

4. 스택 포인터(Stack Pointer)

- 주된 목적으로 서브 루틴 호출이나 인터럽트 발생 시, 다시 돌아올 복귀 주소를 저장하는데 사용

- 이외에 C언어의 지역 변수를 저장, 어셈블리어에서 임시 데이터를 저장하는 용도

- 스택 포인터는 메모리의 상위 번지에서 차례대로 저장

- SPH는 상위 byte, SPL은 하위 byte

- 스택 포인터는 항상 스택의 상단을 가리키는 16bit 레지스터로써, 이는 데이터 저장이 가능한 스택의 번지를 의미한다.

- Push 명령어를 사용하면, 1byte 데이터를 SP가 가리키는 스택메모리 번지에 저장하고 이후 SP값을 1만큼 감소

- Pop 명령어를 사용하면, 먼저 SP값을 1 증가시킨 후에 SP가 가리키는 스택 메모리 번지에서 1byte의 데이터를 꺼냄

5. 메모리 구조

1) 물리적 : 내부 플래시 메모리 / 내부 SRAM / 내부 EEPROM / 외부 SRAM

- 내부 플래시 메모리

: 사용자가 작성한 프로그램 자체가 인텔의 HEX 형태로 적재

- 내부 SRAM

: 사용자가 작성한 프로그램이 동작할 때, 필요한 여러가지 정보를 동적으로 생성

- 내부 EEPROM

: 영구적으로 저장할 필요가 있는 데이터 저장

- 외부 SRAM

: 내부 SRAM만으로는 부족하거나 그 밖의 이유로 확장할 경우 사용

2) 기능적 : 프로그램 메모리 / 데이터 메모리

① 프로그램 메모리

- 8bit 마이크로 컨트롤러이지만,

명령어는 8bit가 아닌, 16bit 구조로 되어 있음.

- 64k × 16bit의 용량을 가짐

- Instruction이 16bit인 경우,

하나의 번지를 / 32 bit인 경우, 2개의 번지를 차지함

- 메모리는 두 부분으로 나뉘는데,

하나는 부트프로그램영역(부트로더),

두 번째는 응용프로그램영역

② SRAM 데이터 메모리(내부)

- 내부 SRAM과 내부 EEPROM으로 나뉨

- 64byte IO메모리는 IN/OUT 명령어로 접근 가능

- 확장된 160byte IO 메모리는 ST/STS/STD와

LD/LDS/LDD 명령어로 접근 가능

- 10,000번 반복 기입 가능

③ EEPROM 데이터 메모리(내부)

- 100,000번 반복적으로 기입 가능

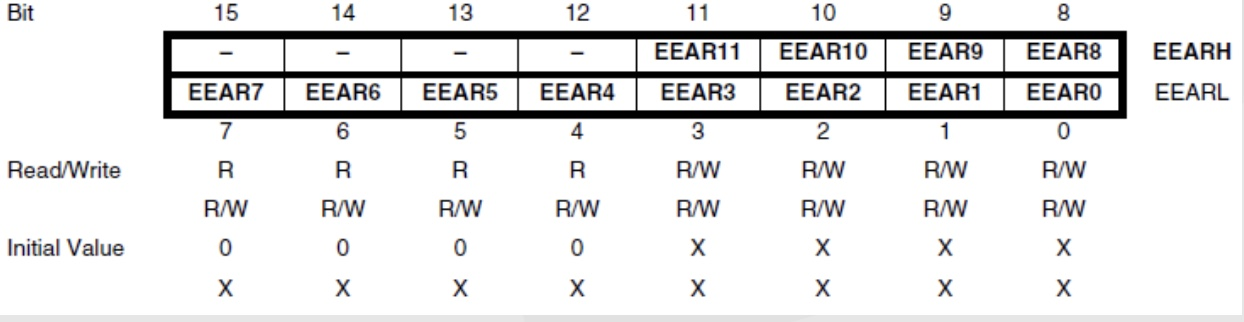

<EEARH(EEARL)>

- Bit 15~12 : 예약 비트

- Bit 11~0 : 내부 EEPROM 4kbyte를 나타내는 address

<EEDR>

- Bit 7~0 : 내부 EEPROM 데이터를 쓰고 읽는 경우에 사용하는 8bit 데이터 레지스터

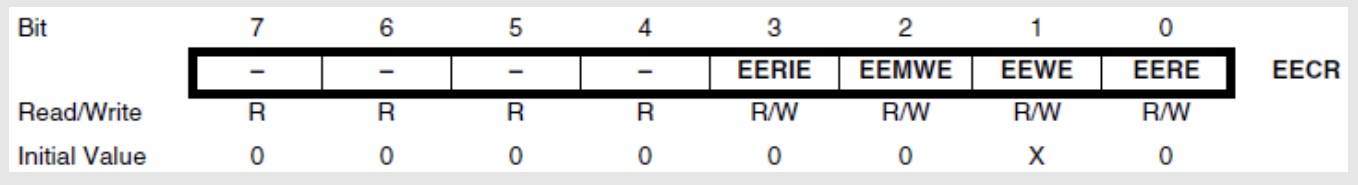

<EECR>

- Bit 3 : EERIE(EEPROM Ready Interrupt Enable)

1로 설정되면, EEWE bit가 0이 될 때 EEPROM reaady 인터럽트 발생하는 기능

- Bit 2 : EEMWE(EEPROM Master Write Enable)

EEWE를 1로 설정할 때, EEPROM에 쓰기가 허용 여부 결정

- Bit 1 : EEWE(EEPROM Write Enable)

EEMWE가 1로 설정되면 EEWE가 1로 되고 나서

4클록 사이클 이내에 EEDR의 데이터를 EEAR이

가리키는 EEPROM의 주소에 쓴다.

완료되면, EEMWE는 자동으로 0이 됨

- Bit 0 : EERE(EEBROM Read Enable)

EEPROM의 읽기 스트로브로서 EEAR 레지스터에 적잘한 주소값이

부여된 경우, EERE를 1로 해야 EEPROM 읽기 시작 가능

④ IO메모리

- 내장된 각종 I/O 장치를 제어하기 위한 레지스터로 IN/OUT 명령을 사용하여 입출력 장치에 접근

Pull-up / Pull-down Resister

1. Floating 현상

스위치가 연결되지 않은 상태에서, 전류가 흐르는지 안 흐르는지 알 수 없는 상태

즉, 신호가 0(low)과 1(high) 사이의 애매한 위치에 떠 있는 현상

디지털 핀을 입력상태로 설정하면, 5V값은 high, 0V값은 low로 인식한다.

그런데 핀 자체의 칩에서는 몇 V인지 인식할 수 없고 입력 단자 주위의 정전기나 noise에 의해 오류가 발생한다.

2. 풀업 저항

: 저항을 전원쪽에 붙여주어 플로팅 현상을 해결하는 방법

그림과 같이 풀업저항에서 스위치가 열린 상태에선 입력 핀으로 전류가 흐르게 되고, 전원 전압과 같은 5V 전압이 걸린다.

∴ 입력 핀에는 high값이 읽이게 됨.

3. 풀다운 저항

: GND에 저항을 연결하여 플로팅 현상을 해결하는 방법

스위치가 열린 상태에서는 어디에도 전류가 흐르지 않고, 입력 핀에는 0V의 전압이 걸린다.

스위치가 닫힌 상태에서는 저항으로 인해 전류가 입력 핀 쪽으로 흐르고 5V의 전압이 걸린다.