[소비 전력]

소비전력에는 크게 두 가지 종류가 있으며,

아래 두 가지를 합쳐, 소비전력으로 나타낸다.

1. Dynamic Power

CMOS에서 On/Off가 되는 순간(Transition이 일어나는 순간)에 소비되는 전력

동적 전력은 용량성 부하(C)가 충/방전하면서 소모되는 전력으로,

트랜지스터의 Short Citcuit 전류(Isc)와 스위칭 전류(Iswitch)에 의해 발생한다.

2. Static Power

누설전류(Leakage Current)를 의미한다.

최근, 공정이 점점 더 미세해지면서 이 문제의 심각성 또한 증가되고 있다.

[Clock Gating]

📌 Clock Gating이란?

Clock gating은 전체 회로가 활성 상태에 있을 때에만 클럭을 공급하는 것이 아니라,

특정 논리 블록이나 레지스터 등이 활성 상태일 때에만 클럭을 공급하는 방식이다.

쉽게 말하면, 비활성 상태의 회로는 클럭을 중지하여 해당 회로의 동작을 일시 정지시킨다는 뜻이다.

사용하지 않는 모듈이더라도 switching되는 clock에 의해 Dynamic power가 발생하게 된다.

PLL에서 모듈까지 clock을 일정하게 전송하기 위해 중간 중간에 있는 Cell들에서 많은 전력이 소모되며

이렇게 불필요한 모듈에 clock이 전달되는 것을 방지하는 방법이 Clock Gating이다.

위와 같은 방식을 사용하면,

전체 클럭이 항상 돌 필요가 없는 부분을 필요한 순간에만 클럭을 활성화함으로써 전력을 절약할 수 있다.

📌 구현 방법

AND gate 활용

Clock Gating은 일반적으로 AND 게이트를 사용해서 구현한다.

활성화 제어 신호와 클럭을 AND 게이트에 연결하여, 활성화되지 않으면 클럭이 차단되도록 설계한다.

module ClockGating_AND ( input clk, // 입력 클럭 input enable, // 활성화 신호 output reg gated_clk // Clock Gating이 적용된 클럭 ); always @(*) begin // AND 게이트를 사용하여 활성화 신호와 클럭을 연결 // 활성화되지 않은 경우에는 클럭이 차단됨 gated_clk = enable & clk; end endmodule

동적 OR gate 활용

활성화 신호가 있을 때에만 클럭을 전달하는 동적 OR 게이트도 사용될 수 있다.

module ClockGating_OR ( input clk, // 입력 클럭 input enable1, enable2, // 활성화 신호 output reg gated_clk // Clock Gating이 적용된 클럭 ); always @(posedge clk) begin // 동적 OR 게이트를 사용하여 활성화 신호들과 클럭을 연결 // 하나 이상의 활성화 신호가 있을 때에만 클럭이 전달됨 if (enable1 | enable2) begin gated_clk <= clk; end end endmodule

📌 Clock Gating의 장점 및 적용 분야

1. 전력 소모의 감소

: 비활성화 상태의 논리 블록에 클럭을 제공하지 않음으로써

해당 부분의 동작을 정지시키고 전력 소모를 줄일 수 있다.

2. 데이터 경로의 불필요한 동작 방지

: 클럭이 차단된 상태에서는 해당 부분의 데이터 경로가 동작하지 않으므로

불필요한 동작을 방지할 수 있다.

3. 주기적인 작업을 수행하는 회로에서 효과적

: 주기적으로 활성화되는 상태와 그렇지 않은 상태가 발생하는 경우에 적용할 수 있다.

📌 Clock Gating 사용 시, 유의사항

Clock Gating이 모든 상황에는 적합하지 않으며, 이를 오용하면 동기화 문제가 발생할 수 있음.

특히, 클럭을 중단하면 해당 부분의 레지스터 값이 변하지 않아야 하는 경우에 주의가 필요하다.

Example

어떤 상태 레지스터 state_reg가 있고, 이 레지스터는 클럭이 동작하는 동안에만 갱신되어야 한다.

Clock Gating을 사용하여 해당 레지스터를 갱신하는 동안에만 클럭을 활성화하는 코드를 작성해보자.

module ClockGating_Example ( input clk, input enable, input [7:0] data_input, output reg [7:0] state_reg ); always @(*) begin // AND 게이트를 사용하여 활성화 신호와 클럭을 연결 // 활성화되지 않은 경우에는 클럭이 차단됨 gated_clk = enable & clk; end wire gated_clk; // 동기화 문제를 방지하기 위해 갱신 동안에만 활성화되는 Clock Gating always @(posedge gated_clk) begin // Clock Gating이 적용된 클럭을 사용하여 상태 레지스터 갱신 if (enable) begin state_reg <= data_input; end end endmodule

✅ 문제점

만약 enable 신호가 동시에 두 번 이상의 클럭 사이클동안 활성화되는 경우,

state_reg는 여러 번 갱신될 수가 있다.

✅ 해결 방법

클럭 플립플롭의 동작을 정확하게 동기화하기 위해,

리셋이나 클리어신호를 사용하면 된다.

module ClockGating_Example ( input clk, input enable, input [7:0] data_input, output reg [7:0] state_reg ); reg gated_clk; // 리셋 신호를 사용하기 위해 reg로 선언 initial begin gated_clk <= 1'b0; // 리셋 신호 초기화 end always @(*) begin // AND 게이트를 사용하여 활성화 신호와 클럭을 연결 // 활성화되지 않은 경우에는 클럭이 차단됨 gated_clk = enable & clk; end // 동기화 문제를 방지하기 위해 갱신 동안에만 활성화되는 Clock Gating always @(posedge gated_clk) begin // Clock Gating이 적용된 클럭을 사용하여 상태 레지스터 갱신 if (enable) begin state_reg <= data_input; end end endmodule

이렇게 하면, 시스템 시작 시 gated_clk 가 0으로 초기화된다.

그 후에는 gated_clk가 상승 엣지일 때랑, enable 신호가 활성화될 때,

state_reg를 갱신하게 되어 동기화를 강화시킬 수 있다.

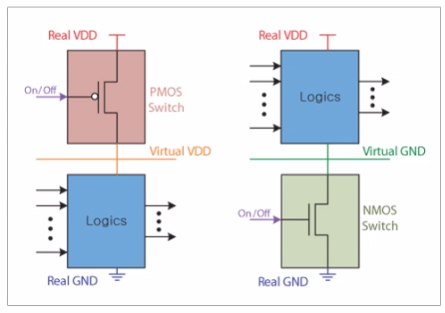

[Power Gating]

📌 Power Gating이란?

비활성 상태의 블록이나 회로를 전원에서 분리하여, 전력 소비를 최소화하는 방법

특히, 모바일 디바이스나 저전력 임베디드 시스템과 같은 에너지 효율이 중요한 응용 분야에서 많이 사용한다.

📌 Power Gating의 특징

1. 전력 소비 감소 및 에너지 효율 향상

: 비활성 상태의 블록이나 회로의 전원을 차단함으로써

전력 소모를 줄이고 에너지 효윻을 향상시킬 수 있다.

2. 동적 전력 소모 감소

: Power Gating은 주로 정적인 상태에서의 전력 소모를 감소시키는데,

일부 경우에는 동적인 상태에서도 효과를 발휘할 수 있다.

3. 전력 관리에 용이

: 전력 관리 정책에 따라 필요한 블록들을 동적으로 활성화하거나

비활성화함으로써 시스템의 전력 소비를 더욱 효과적으로 관리할 수 있다.

📌 Power Gating의 구현 방법

아래 코드는 enable 신호에 따라 동작하는 Power Gating의 간단한 예시이다.

실제로는 시스템의 요구 사항에 따라 세부적으로 수정할 필요가 있다.

module PowerGating_Example ( input clk, input enable, output logic_out ); reg [31:0] counter; // 카운터 레지스터 // Power Gating을 위한 비활성화 가능한 블록 reg [7:0] power_gated_block; // 활성화 및 비활성화 상태를 나타내는 상태 변수 reg power_gating_enabled; // 동적 전력 소비를 줄이기 위해 Power Gating된 블록을 비활성화 always @(posedge clk) begin if (enable && power_gating_enabled) power_gated_block <= 8'b0; // 비활성화 상태로 설정 else power_gated_block <= counter; // 블록이 활성화된 경우 카운터 값 저장 end // 다른 동작을 수행하는 로직 (예: 실제 사용되는 로직) always @(posedge clk) begin if (enable && power_gating_enabled) logic_out <= 1'b0; // Power Gating된 상태에서 로직을 비활성화 else logic_out <= (counter == 8'hFF); // 예시로 카운터가 최대값에 도달하면 로직 활성화 end // Power Gating 상태를 제어 always @(posedge clk) begin if (enable) power_gating_enabled <= 1'b1; // Power Gating 활성화 else power_gating_enabled <= 1'b0; // Power Gating 비활성화 end endmodule

cf) generate문을 써서 모듈을 활성/비활성하는 것도 저전력 설계인가?

저전력 설계라고 보기 어렵다.

generate문은 주로 디자인의 일부를 조건부로 생성하는데 사용되며,

단순히 코드의 일부를 조건부로 생성하거나 포함시키는 것에 불과하다.

즉, 그 자체로 회로의 활성/비활성 상태를 관리하지 않는다는 의미.

generate문 예시

module TopModule ( input top_input_a, input top_input_b, output top_output_c ); `define ENABLE_MODULE // 모듈을 활성화하는 generate 문 generate `ifdef ENABLE_MODULE // ENABLE_MODULE이 정의되어 있을 때만 이 블록이 생성 MyModule my_module_inst ( .input_a(top_input_a), .input_b(top_input_b), .output_c(top_output_c) ); `endif endgenerate // 나머지 TopModule의 코드 endmodule

참 조

https://blog.naver.com/PostView.naver?blogId=zzbksk&logNo=221422605046

'# Semiconductor > - FPGA 관련 지식' 카테고리의 다른 글

| [FPGA] RTL에서의 저전력 설계 방법(2/2) - Multi Vth, Multi Vdd, DVFS (1) | 2023.12.08 |

|---|---|

| H/W 통신 프로토콜의 모든 것 Part.1 - UART, SPI, I2C (1) | 2023.12.07 |

| [FPGA] FPGA, ASIC, SoC의 차이점 (0) | 2023.09.23 |

| [FPGA] Hardware Design의 이해, RTL과 FPGA란? (1) | 2023.09.20 |