[RTL]

📌 RTL이란?

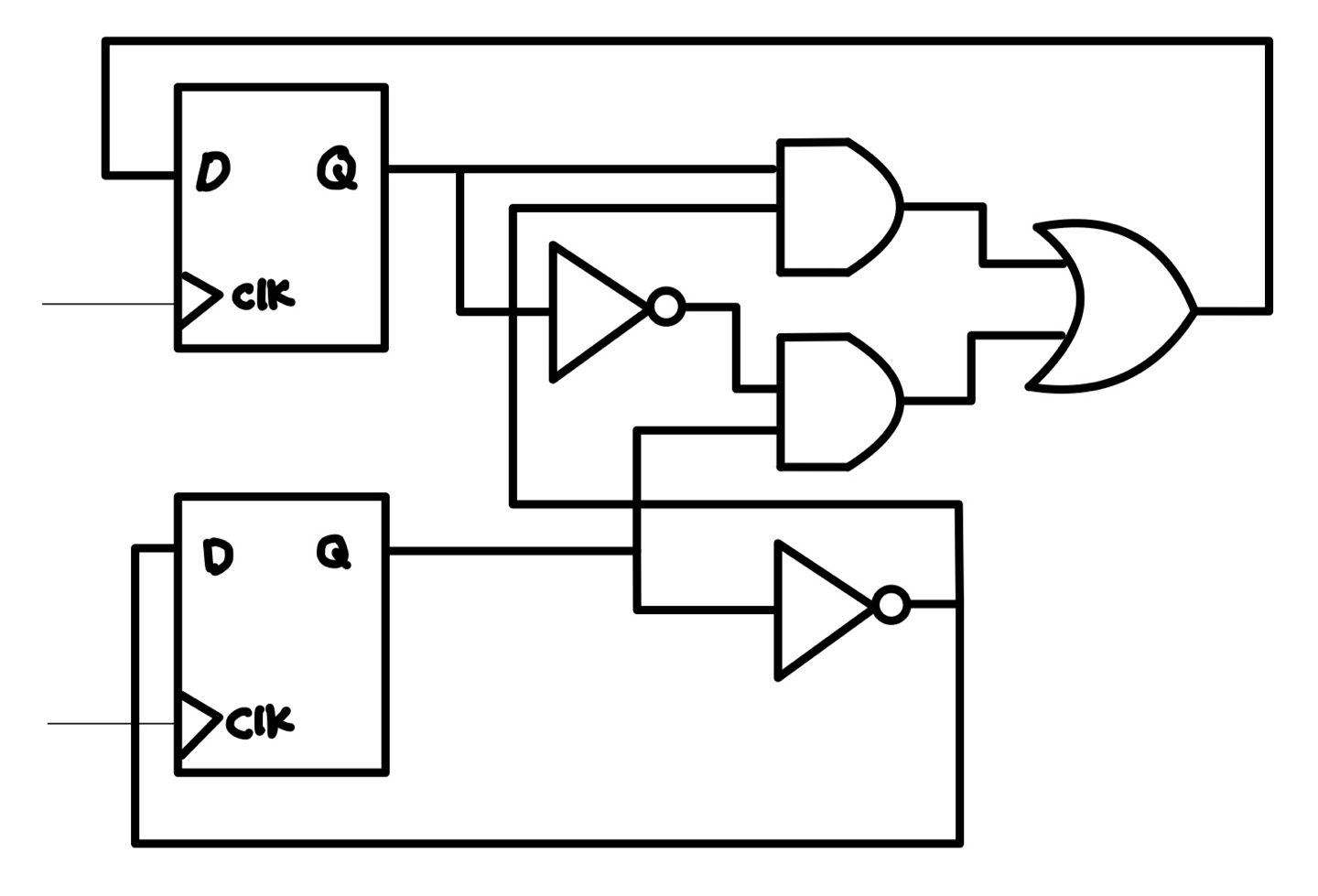

FPGA를 알아보기에 앞서, RTL에 대해 먼저 알아보도록 하자.

RTL은 Register Transfer Level의 약어로,

레지스터와 로직 회로를 이용하여 Synchronous 디지털 회로를 설계하는 레벨을 의미하며,

위 그림과 같이 Flip-Flop을 이용한 레지스터와 Gate 등의 로직회로로 구성된 디자인을 RTL이라 한다.

RTL 디자인은 디지털 회로를 레지스터 및 데이터 전달 단위로 추상화하는 방법이고

RTL 수준에서 디자인하면 회로를 간단하게 기술할 수 있으며,

고수준 설계에서 하드웨어로 변환하기 위한 중간 단계로 사용된다.

📌 RTL의 주요 요소들

1. 레지스터

: 레지스터는 데이터를 저장하는 디지털 메모리 요소이며,

데이터가 레지스터에 저장되고 다른 레지스터로 전달되는 등의 데이터 이동이 일어난다.

2. 데이터 전달

: RTL 수준에서는 데이터가 레지스터 간 어떻게 전달되는지를 중심으로 설계한다.

이러한 데이터 전달은 논리게이트, MUX 등을 사용하여 구현한다.

3. 평행 연산(Parallel Operation)

: RTL 디자인은 다양한 연산과 논리 게이트의 평행 동작을 표현한다.

즉, begin-end로 구성된 블록 내 이외에는 병렬적으로 동작한다는 뜻이다.

이러한 특징덕분에 동시에 여러 연산을 수행할 수 있고 속도면에서 상당한 강점을 가진다.

4. 언어

: RTL 디자인을 표현하기 위해서

VHDL(VHSIC Hardware Description Language)나 Verilog와 같은

하드웨어 기술 언어가 주로 사용된다.

[FPGA]

📌 FPGA란?

Field Programmable Gate Arrary의 약자로,

디지털 논리 회로를 사용자가 프로그래밍하여 원하는 기능을 수행할 수 있는 하드웨어 플랫폼이다.

FPGA라는 그 이름에서도 알 수 있듯이, 프로그램 가능한 논리 소자의 배열을 의미하고

우리가 원하는 설계를 하려면 HDL(Hardware Description Language)를 사용해야 하며,

여기서 가장 대표적인 HDL은 Verilog와 VHDL이다.

H/W Engineer는 HDL을 활용하여 논리회로를 원하는 의도에 맞춰 동작하게 설계한 후

bitstream을 변환 후 FPGA를 구성하여 사용한다.

요약하면, 디지털 회로를 마치 프로그램하듯이 설계할 수 있도록 만들어진 반도체 칩을 의미한다.

📌 FPGA의 구조

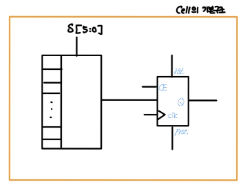

1. Logic Block(CLB, Configurable Logic Block)

: 로직 블록은 FlipFlop, LUT, MUX 등으로 구성되어 있고,

이들을 활용하여 로직 게이트를 자유자재로 구현할 수 있다.

2. Programmable Interconnect(배선)

: FPGA의 특징 중 하나로, 내부 결선을 자유롭게 직접 변경하여 사용할 수 있기 때문에

User의 용도에 맞게 설계가 가능하다.

3. I/O Block

: Peripheral과의 데이터 및 Signal 교환을 담당하는 부분이며,

교환 방식은 Pysical 방식과 Logical 방식으로 나뉜다.

- Pysical I/O : 핀의 전압 레벨, 전류, 트랜시버, 입출력 표준 및 물리적인 레이아웃 고려

- Logical I/O : 어떤 핀에서 데이터를 읽거나 쓰고, 어떻게 처리되는지를 기술하며,

RTL 디자인에서 Logical 방식으로 I/O 신호를 다룬다.

4. Block RAM

: 위 그림처럼 Cell 하나는 LUT와 DFF로 구성되어있다.

Register는 되먹임 구조가 아니기 때문에 LUT이 필요없고

만약 Memory를 만들기 위해서 DFF를 사용하면

옆에 있는 LUT도 같이 할당되어 사용이 불가하게 된다.

고수준 설계로 가면 수많은 LUT이 필요하게 되는데,

이렇게 낭비되는 상황을 방지하기 위해서 RAM Block이 따로 마련되어 있고

Memory로 사용되는 DFF는 이 영역에서 할당이 된다.

5. CMT(Clock Management Tile)

: 클럭 신호를 관리하고 분배하는 요소이며,

다양한 클럭 도메인 간의 시간 동기화를 유지하고

클럭 신호를 주파수 및 위상에 따라 조정하는 역할을 한다.

📌 RTL과 FPGA의 상관관계

FPGA는 RTL 디자인을 실행하는 하드웨어 플랫폼이다.

FPGA는 디지털 회로를 프로그래밍 가능한 하드웨어로 구현할 수 있는 장치이며,

RTL 디자인은 FPGA에 프로그래밍되어 FPGA 내부의 리소스, 특히 CLB와 레지스터를 구성하고 제어하고

FPGA에 로드하면 FPGA는 해당 디자인을 실행하고 하드웨어 수준에서 동작한다.

RTL은 FPGA 디자인 중 하나의 Level이다.

FPGA 디자인은 다양한 단계의 추상화 Level로 표현할 수 있고

RTL은 그 중 하나로서, 하드웨어의 레지스터와 데이터 전달 단위를 중심으로 디자인을 기술하는 Level이다.

RTL은 FPGA 디자인의 중간 단계로 사용되며, 고수준 디자인(C/C++로 작성된 설계)에서

하드웨어로의 변환 과정 중 하나이다.

RTL 디자인 언어

RTL 디자인은 주로 하드웨어 설계 언어인 VHDL 또는 Verilog를 사용하여 표현되며,

이러한 언어로 작성된 RTL 코드는 FPGA 도구를 통해 물리적인 하드웨어 구현으로 컴파일된다.

프로그래밍 가능성

FPGA는 다양한 응용 분야에서 사용되며,

RTL 디자인을 변경하거나 업데이트하여 새로운 기능을 추가하거나 수정할 수 있다.

이러한 유연성은 FPGA가 다양한 어플리케이션에 사용되는 이유 중 하나이다.

요약하면,

FPGA는 RTL 디자인을 실행하는 하드웨어 플랫폼이며

RTL은 디자인의 중요한 구성요소로서 하드웨어 레벨의 동작을 설명하는데 사용된다.

FPGA를 사용하면 RTL 디자인을 하드웨어로 변환하고 프로그래밍 가능한 하드웨어 플랫폼에서 실행할 수 있다.

'# Semiconductor > - FPGA 관련 지식' 카테고리의 다른 글

| [FPGA] RTL에서의 저전력 설계 방법(2/2) - Multi Vth, Multi Vdd, DVFS (1) | 2023.12.08 |

|---|---|

| [FPGA] RTL에서의 저전력 설계 방법(1/2) - Clock Gating, Power Gating (0) | 2023.12.08 |

| H/W 통신 프로토콜의 모든 것 Part.1 - UART, SPI, I2C (1) | 2023.12.07 |

| [FPGA] FPGA, ASIC, SoC의 차이점 (0) | 2023.09.23 |