[CPU란?]

📌 CPU란?

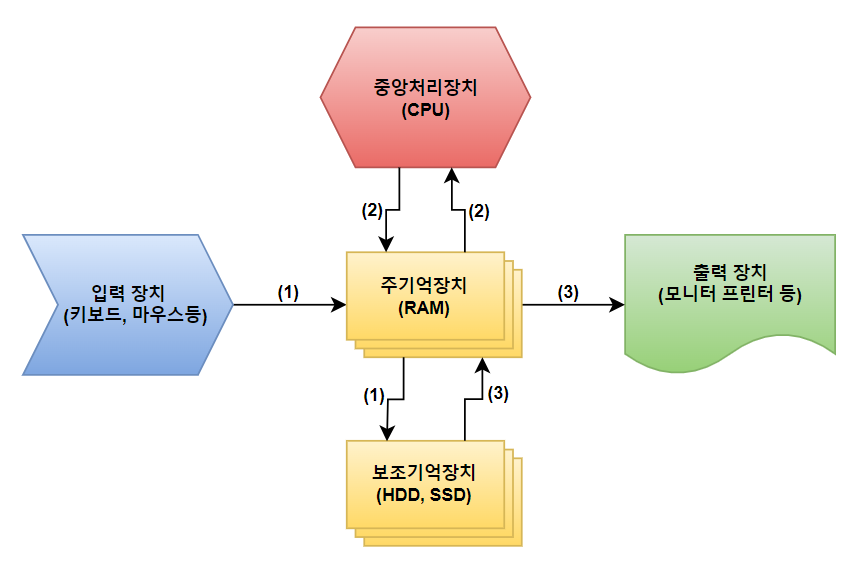

중앙처리장치(CPU)는 Centrol Processing Unit의 약자로,

컴퓨터에서 명령어를 해석하고 실행하는 역할읋 하는 마이크로 프로세서이며,

명령어의 해석과 자료의 연산, 비교등의 처리를 제어하는 컴퓨터 시스템의 핵심장치이다.

다양한 입력 장치로부터 정보를 입력받아 처리한 후,

그 결과를 출력장치로 보내는 일련의 과정을 제어하고 조정하는 일을 수행한다.

[CPU의 구성 요소]

CPU는 아래 그림과 같이

Control Unit(제어장치), ALU(연산 장치), Register(레지스터)

로 구성되어 있고 각 구성 요소들은 Data Bus를 통해서 데이터를 주고받는다.

📌 Control Unit(CU, 제어 장치)

- CU는말 그대로 CPU를 컨트롤하는 장치이다.

ROM(기억 장치)으로부터 프로그램 명령어를 순차적으로 꺼내 해석하고

헤석한 명령어에 따라 어떤 작업을 수행해야 하는지 결정하며,

이때, CU는 실행에 필요한 제어 신호를 기억장치, 연산장치, 입출력장치 등으로

전달하여 명령을 수행하도록 한다.

- CU는 PC(프로그램 카운터), 명령 해독기, 부호기, 명령 레지스터 등으로 구성된다.

<PC>

PC는 Program Counter로 현재 실행 중인 프로그램의 다음 명령어 위치를 가리키는 레지스터이다.

CPU는 PC가 가리키는 명령어를 실행하고, 그 후에 PC를 증가시켜 다음 명령어의 위치를 가리키며

이러한 PC로 인해, CPU는 명령어를 순차적으로 실행할 수 있다.

이전 값을 기반으로 다음 값이 카운트되므로, Loadable Counter로 설계되어야 한다.

<MAR>

MAR은 메모리 주소 레지스터로 CPU가 메모리에서 데이터를 읽거나 쓸 때 사용된다.

CPU가 메모리를 액세스할 주소를 MAR에 저장하고,

이 주소를 기반으로 메모리와 상호작용한다.

<MDR>

MDR은 메모리 데이터 레지스터로, 메모리에서 읽어온 데이터나 메모리에 쓸 데이터를 임시로 저장하며,

CPU와 메모리 간의 데이터 교환을 수행하는 중요한 역할을 한다.

<IR>

IR은 Instruction Register의 약자로 명령어 레지스터를 의미하고 현재 실행 중인 명령어를 저장하며,

CPU는 IR에 저장된 명령어를 디코딩하고 실행하게 된다.

<Control Block>

제어 블록은 CPU의 동작을 제어하는 데 사용되는 논리 회로나 레지스터의 집합이다.

이는 명령어 실행, 레지스터 간의 데이터 이동, 연산 수행 등 CPU의 기능을 조절하고 동기화하하며

명령어의 디코딩과 실행을 가능하도록 하는 CPU의 핵심 구성 요소이다.

여러 모듈에서 동시에 버스로 데이터를 전송하면, 충돌이 발생하게 된다.

이러한 문제를 방지하기 위해 출력은 한 번에 한 모듈만 버스로 내보내야 하고

이때, 버스로 입력되는 데이터들의 전송 Enable 신호는 Control block에서 관리한다.

(Enable된 것만 출력하고 나머지는 다 임피던스 출력)

📌 ALU(Arithmetic and Logical Unit, 연산 장치)

- 명령어를 실행하기 위한 산술 및 논리 연산을 수행하는 역할을 한다.

덧셈, 뺼셈과 같은 산술연산 뿐만 아니라, 논리 연산(AND, OR, XOR 등) 도 처리가 가능하고

ALU의 결과는 레지스터에 저장되거나 다음 단계로 전달된다.

- 가산기, 누산기, 데이터 레지스터 드으로 구성된다.

<ACC>

ACC는 Accumulator(누산기)로 CPU 내부에 위치한 레지스터 중 하나이이며,

주로 CPU의 명령어에 따라 데이터를 읽어오고 산솔 및 논리 연산의 중간 결과를 저장하는 데 사용된다

예를 들어, 연속적인 덧셈 연산을 수행할 때, ACC에 현재까지의 덧셈 결과에 더하는 방식으로 진행된다.

<BREG>

BREG는 버퍼 레지스터로, 데이터를 임시로 저장하고 전송하는 데 사용되는 레지스터이다.

예를 들어, 데이터를 메모리에서 CPU로 로드하거나, CPU에서 메모리로 데이터를 보낼 때,

중간 단계로 BREG를 사용할 수 있으며, 이는 데이터의 안정적인 전송과 처리를 돕는 역할을 한다.

<산술 연산 예시>

4 + 7 계산

ACC에 4 저장, BREG에 7 저장

ALU에서 각각 값을 받아서 연산한 뒤에 ACC에 전달하고

연산이 종료되었다면, 그 값을 Data Bus로 전송

📌 Register(레지스터)

- CPU 내부에 있는 소규모 고속 기억 장치이고

명령어 주소, 코드, 연산에 필요한 데이터, 연산 결과 등을 임시로 저장하는 기능을 한다.

레지스터는 메모리 계층의 최상위에 위치하며, 가장 빠른 속도로 접근이 가능한 메모리이며,

용도에 따라 범용 레지스터와 특수 목적 레지스터로 구분된다.

<TMPREG>

Temporary Register로 일시적으로 데이터를 저장하고 처리하는 데 사용되며,

주로 중간 계산의 결과를 저장하거나 데이터를 임시로 보관하는 데 활용된다.

TMPREG는 CPU의 연산 동안 임시 데이터 스토리지로 사용될 수 있다.

<CREG>

Control Register는 시스템의 제어 및 설정을 관리하기 위해 사용되는 레지스터이다.

시스템 설정, 모드 전환, 예외 처리 및 다른 중요한 제어 동작을 수행하기 위해 사용되며,

예를 들어 프로세서 모드 변경, 인터럽트 활성화/비활성화 및 보안 성정을 관리하는 데 사용될 수 있다.

<RREG>

General-Purpose Register는 일반 목적 레지스터로, 다양한 연산 및 데이터 저장에 사용되고

주로 프로그램 카운터, 스택 포인터, 범용 데이터 저장 등 다양한 목적으로 활용된다.

프로세서 아키텍쳐에 따라 여러 개의 RREG가 존재할 수 있으며, 주로 프로그래머가 직접 접근하여 데이터를 조작한다.

<OUTREG>

Output Register는 데이터 출력과 관련된 작업을 수행하는 데 사용되는 레지스터이고

주로 입출력 연산, 데이터 전송, 디스플레이 제어 및 통신과 관련된 작업에서 활용되며,

외부 장치와 데이터를 주고받는 데에 OUTREG를 사용할 수 있다.

[CPU의 동작 원리]

📌 CPU의 연산 과정

CPU의 연산은 Fetch - Decode - Execute - Writevack으로 총 4단계로 이루어진다.

i) Fetch(인출) : 메모리상의 PC(프로그램카운터)가 가리키는 명영어를 CPU로 인출하여 Reg에 적재

ii) Decode(해석) : 명령어의 해석, 해당 단계에서 명령어의 종류와 타겟 등을 판단한다.

iii) Execute(실행) : 해석된 명령어에 따라 데이터에 대한 연산을 수행한다.

iv) Writeback(쓰기) : 명령어대로 처리 완료된 데이터를 메모리에 기록한다.

(1) : 보조기억장치에서 저장된 프로그램을 읽거나, 입력장치에서 입력받은 데이터를 주기억장치에서 읽는다.

(2) : 주기억장치에서 읽어온 데이터를 중앙처리장치(CPU)가 읽고 처리한 후, 다시 주기억장치로 전송한다.

(3) : 주기억장치는 연산된 데이터를 출력 장치에 보내거나 보조기억장치에 저장한다.

(4) : 제어장치는 (1)~(3) 과정에서 명령어가 순서대로 잘 실행되도록 제어하는 역할을 한다.

📌 명령어 사이클

CPU에서는 프로그램을 실행하기 위해 주기억장치에서 명령어를 순차적으로 인출 - 해독 - 실행하는 과정을 반복하는데,

CPU가 주기억장치에서 한 번에 하나의 명령어를 인출하고 실행하는 일련의 활동을 명령어 사이클(Instruction Cycle)이라 한다.

명령어 사이클은 인출 사이클, 실행 사이클, 간접 사이클, 인터럽트 사이클로 세분화시킬 수 있는데,

인출 사이클과 실행 사이클은 항상 수행되지만

간접 사이클과 인터럽트 사이클은 주소 지정방식이 필요할 때나 인터럽트 요구가 발생했을 때만 수행된다.

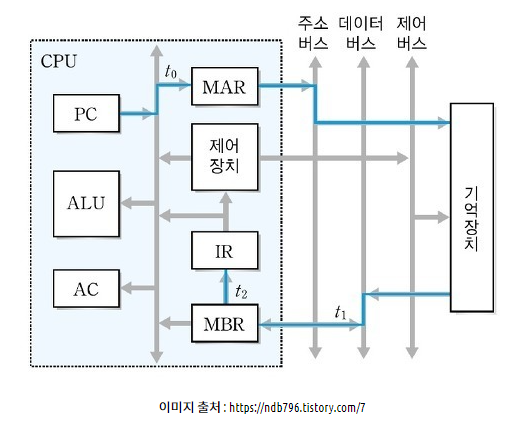

✅ Fetch Cycle(인출 과정)

<Fetch(패치, =읽기) : 메모리에서 명령어를 가져오는 과정>

Counter는 ROM에서 명령어를 불러올 때 마다 1씩 증가하고

우리는 명령어를 통해 ROM에 저장된 어셈블리어를하나씩 꺼내서 사용하는데,

(ROM에 저장되는 어셈블리어도 CPU를 만드는 사람이 다 작성해줘야 한다.)

이때 PC를 통해 명령어에 해당하는 어셈블리어의 위치를 가리킨다.

PC가 가리킨 위치의 주소가 MAR에 저장되고 저장된 주소에 맞는 데이터를

MDR에 임시저장한 뒤 내보내게 된다.

MDR에서 내보내진 명령어는 IR에서 저장된 뒤, Control Block을 통해

디코딩되어 명령을 수행한다.

간추리면,

i) PC(프로그램 카운터)에 저장된 주소를 MAR로 전달한다.

ii) MAR에 저장된 내용을 토대로 주기억장치의 해당 주소에서 명령어를 인출한다.

iii) 인출한 명령어를 MBR에 저장한다.

iv) 다음 명령어를 인출하기 위해 PC의 값을 증가시킨다.

v) MBR에 저장된 내용을 IR에 전달한다.

// 이렇게 표현하기도 한다.

T0 : MAR <- PC

T1 : MBR <- M[MAR], PC <- PC + 1

T2 : IR <- MBR

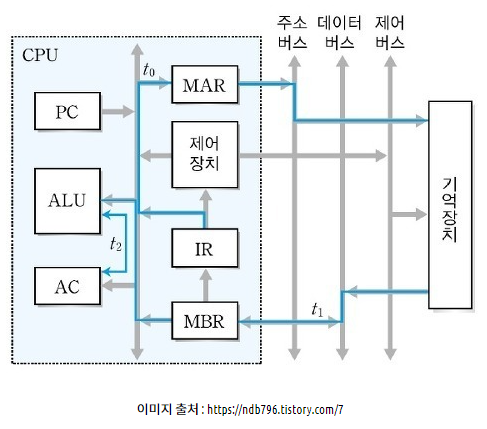

✅ Execute cycle(실행 과정)

i) IR(명령어 레지스터)의 내용을 MAR로 전달한다.

ii) 메모리에 저장된 데이터값을 MBR에 저장한다.

iii) AC(누산기)에 저장된 값에 명령한 연산을 실행한다.

참조 : CPU의 구조와 원리 by AndroidTeacher

'# Programming > - Embedded 관련 지식' 카테고리의 다른 글

| 신개념 컴퓨터 아키텍쳐, CXL이란? (0) | 2023.09.20 |

|---|---|

| 임베디드 시스템의 핵심 기술, RTOS란? - Part.2 (CPU 동작 단계, CPU Scheduling, Process, Task vs Thread) (0) | 2023.09.04 |

| 공유 자원을 관리하는 두 가지 방법 : Mutex / Semaphore (0) | 2023.09.01 |

| OS(운영체제)의 핵심 엔진 - Kernel(커널)의 기능과 구조, Scheduling Algorithm, Context Switching (0) | 2023.08.31 |

| Computer Architecture, RISC & CISC란? (0) | 2023.08.17 |