본 게시글은 이병진 교수님의 CMOS VLSI DESIGN을 참조하여 작성하였다.

[CMOS VLSI Design 개요]

목적 : CMOS Chip이 어떻게 설계되는지에 대한 이해

📌 IC

정의 : 수 많은 트랜지스터를 하나의 칩 안에 집적시켜 놓은 회로

이전에는 전자회로 기판에 여러 가지 소자(수동과 능동)들을 wire로 연결하여 사용하였다,

IC는 비교적 커다란 전자 회로 기판의 부품들을 Chip 하나에 다 구현한 것으로

Integrated Circuit이라고 부른다

이러한 IC의 장점은 세가지가 있다.

① 속도가 빠르다(Fast)

② 대량 생산이 가능하여 가격이 저렴하다(Cheap)

③ 저전력 운용이 가능하다(Low Power)

위와 같은 장점

라디오와 MP3가 대표적인 예시이다.

전자회로 기판을 사용한 라디오에서 IC를 활용한 MP3로 넘어오면서

굉장히 많은 장점들이 나타나고 있다.

📌 VLSI

SI는 회로 설계 시, 칩의 Size에 따라 구분된다.

- SSI (Small Scale Integration)

- MSI (Middle Scale Integration)

- LSI (Large Scale Integration)

- VLSI (Very Large Scale Integration)

- ULSI (Ultra Scale Integration)

- SoC (System on Chip)

📌 CMOS

CMOS는 Contemorary MOS의 약자로, 상부형(서로 반대의 성질을 가지고 있는)이라는 뜻을 가지고 있다.

nMOS와 pMOS 두 가지로 나뉘며, 각각은 반대의 성질을 가지고 크기 및 에너지는 동등하게 사용되는 트랜지스터이다.

CMOS의 장점은 IC의 장점과 같이 Fast, Cheap, Low Power이다.

CMOS Chip을 설계함에 있어, 꼭 알고 있어야할 선행 지식이 있는데 다음과 같다.

① CMOS 트랜지스터의 동작 및 제조 과정 등의 특성에 대한 지식

② 트랜지스터를 활용하여 어떻게 논리 게이트가 만들어지는지, 논리 회로에 대한 이해

③ 어떻게 레이아웃을 구성할 지

먼저 Layout의 과정은

위 순서대로 이루어지고,

크게 Schematic - Simulation - Layout - DRC - LVS 의 순서로 진행된다.

[Silicon]

📌 Si & 공유결합

일반적으로 원소는 1족부터 8족으로 구분되고,

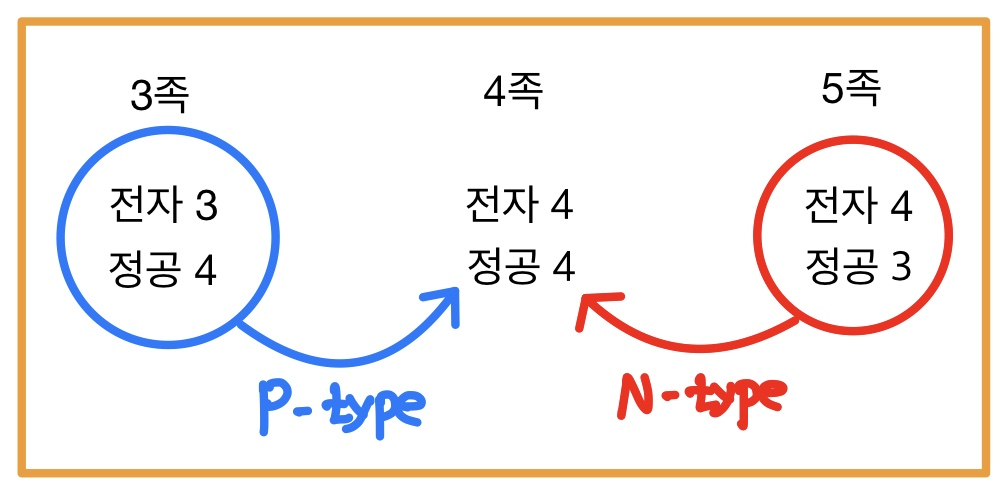

우리가 다루게될 반도체에 사용되는 원소는 3족, 4족, 5족 원소이며,

n족은 전자의 갯수가 n개라 생각하면 되고, 반도체의 대부분을 구성하는 Si는 4족 원소이다.

4족 원소는 쉽게 말하자면, 전자가 4개, 정공이 4개로 수가 같은 원소를 의미하는데,

여기서 짚고 넘어가야될 이론이 두 가지가 있다.

첫 번째는 전자의 전기량과 정공의 전기량 중 어느 것이 더 크냐? 의 문제로,

전자와 정공이 결합하여 중성이 되려면 서로의 전기량은 같아야 하며,

실제로 전자의 전기량은 -1.6x10^-19, 정공의 전기량은 +1.6x10^-19으로 부호만 다르지 절대값은 같다.

두 번째로 이동도(모빌리티)에 관한 내용인데,

똑같이 몸무게가 60kg이 나가는 남성과 여성이 있다.

반례가 있긴 하겠지만, 100m 달리기를 한다면 거의 대부분의 경우 남성이 훨씬 빠를 것이다.

이를 식으로 표시하면, μ남 = μ여 x 2 로 나타낼 수 있고

위 예시와 유사하게, 모빌리티 μ는 전자가 정공보다 약 2~3배정도 빠르다.

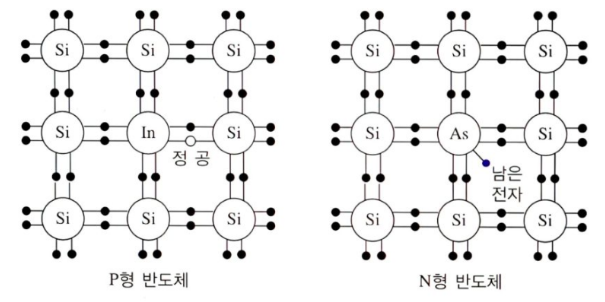

Si 원자들은 4족 원소로서,

서로 간의 전자를 공유하여 8개의 전자가 충족되고 안정된 상태가 된다.

이를 공유결합이라하며, 안정된 상태이므로 전자가 쉽게 빠지지 않는다

→ 부도체이며 여기서 진성 반도체는 부도체이다.

📌 P /N type Semiconductor

위와 같은 진성 반도체(부도체)가 도체의 성질을 띄도록 바꿔보자

이러한 4족 원소들 사이에 3족 또는 5족의 원소들을 첨가(도핑)하면,

전자가 하나 부족하거나(N-type) 하나 남는(P-type) 현상이 발생한다.

이때, P-type의 다수캐리어는 정공, 소수캐리어는 전자가 되고

N-type의 다수캐리어는 전자, 소수캐리어는 정공이 된다.

cf) 반도체의 실리콘과 공사장에서 쓰는 실리콘은 같은 실리콘일까?

정답 : No

해설 : 공사장에서 사용하는 실리콘은 Silicone 과 같이 단어에 e가 붙어 있다.

위와 같이 구분한 이유는 탄소 등 불순물들이 많이 섞인 실리콘이라는 뜻이며,

반도체에 사용되는 실리콘은 Si 함량 99.9999999999%의

순도 높은 진성 실리콘이다.

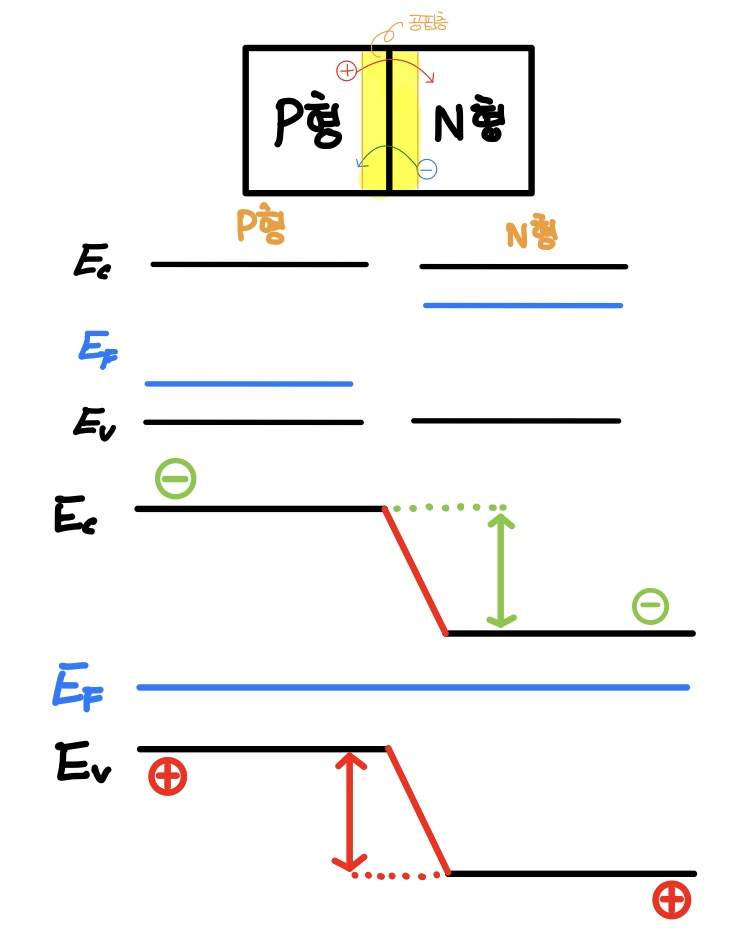

📌 PN Junction

PN Junction은 P형과 N형 반도체를 접합 시킨 것을 뜻한다.

Junction은 어떤 의미를 가지느냐?

에너지 밴드를 보면,

p형은 페르미 레벨이 아래 쪽에, n형은 위쪽에 위치한다.

접합을 하면, 두 반도체의 페르미 레벨이 같아지게 되고

Conduction Band와 Valance Band 간의 층이 형성된다.

이떄, 전자나 정공이 층의 높이만큼 이동하려 한다면 그만한 에너지가 있어야 되고

이 것을 PN접합에서 표현한 것이 바로 공핍층, Depletion Region이다.

[능동 소자]

능동 소자는 Diode, BJT, MOSFET 등이 있고

각 소자는 명칭이 있는 단자를 가지며, 이는 구분할 수 있는 극성이 존재한다는 뜻이다.

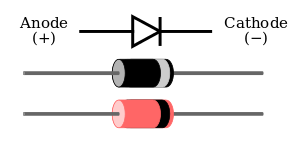

Diode는 Anode, Cathode

BJT는 Emitter, Base, Collector

FET는 Gate, Source, Drain, Body(Bulk)

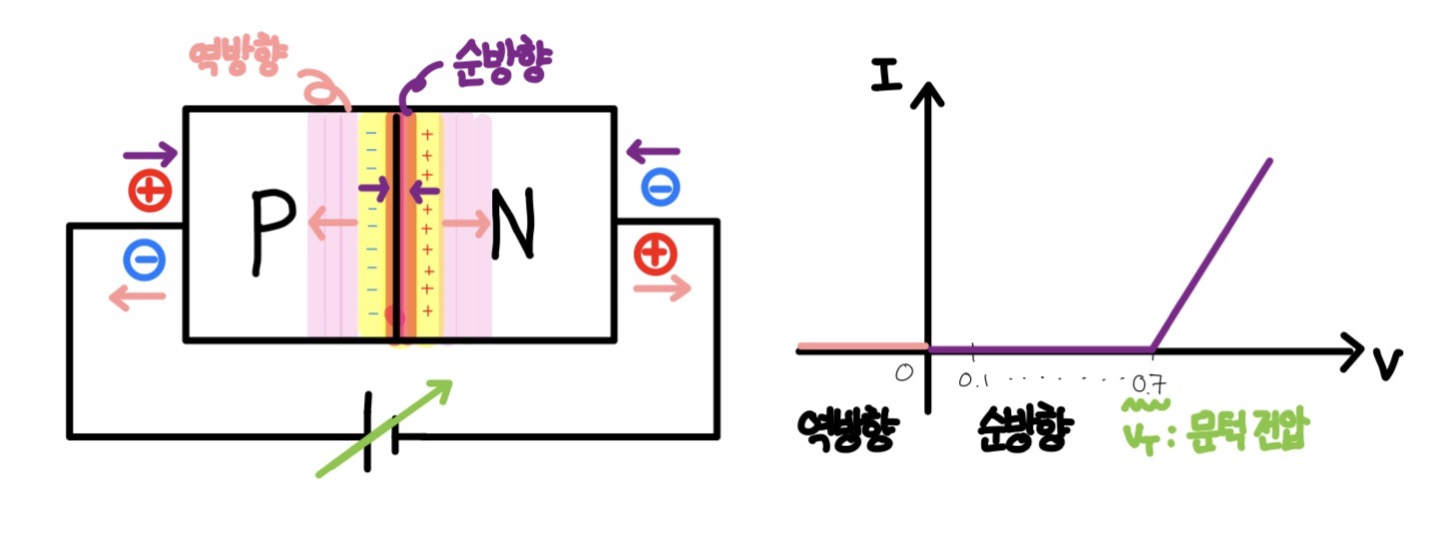

📌 Diode

: 주로 전류를 한쪽 방향으로만 흐르게 하는 정류 작용을 한다.

(한 쪽에는 낮은 저항, 다른 쪽에 높은 저항)

- 가장 많이 쓰는 PN접합 다이오드는 반도체 기반 회로를 구성하는 기본 단위

순방향 바이어스를 걸어주면,

P형에는 정공이 / N형에는 전자가 공급되어 공핍층이 줄어들게 되고

문턱전압인 0.7V 이상의 전압이 인가되면 도통되어 전기가 흐르게 된다.

역방향 바이어스를 걸어주면,

P형에는 전자가 공급되어 정공을 가져가고 N형에는 정공이 공급되어 전자를 가져간다.

따라서 공핍층이 더욱 더 넓어지게 되고 전기는 차단된다.

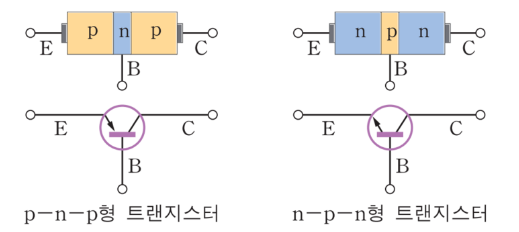

📌 BJT

BJT는 Bipolar Junction Transistor의 약자로,

반도체 3개를 합쳐놓은 반도체 소자이다.

Emitter - Base - Collector로 총 3개의 다리를 가지고 있고, 고주파 특성이 좋다는 장점이 있다.

저 화살표 방향때문에 맨날 헷갈리는데,

베이스에 화살맞은쪽이 피가 많이 나니까 PNP 형이라 외우면 됨.

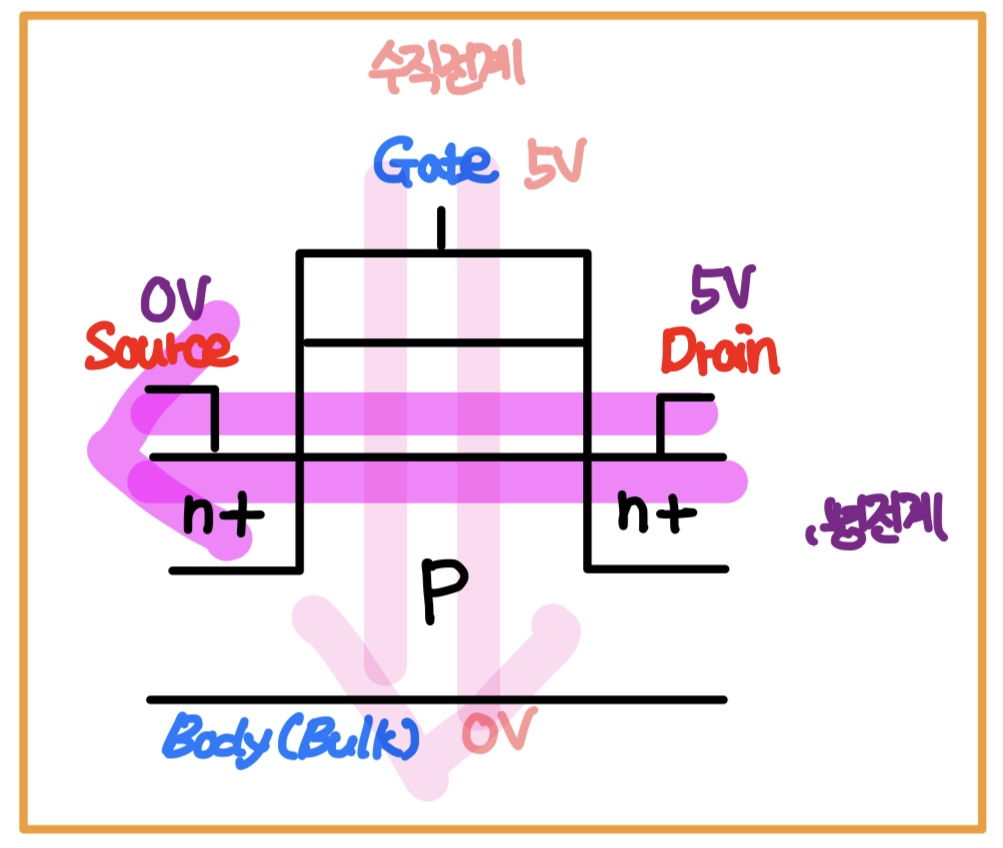

📌 FET(MOSFET)

FET은 일단 MOSFET만 알면 90%는 먹고 들어간다고 보면 된다.

MOSFET은 Metal-Oxide-Semoconductor Field-Effect-Transistor 의 약자로,

MOS와 FET을 결합한 반도체 소자이다.

먼저 MOS는 금속과 반도체 사이에 부도체가 들어있는 적층 구조라는 의미이며,

Oxide의 유전률이 MOS의 특성을 결정짓는다.

FET는 전계효과를 활용하여 전압을 증폭시키는 트랜지스터를 의미하는데,

개념만 들으면 솔직히 잘 이해가 되지 않는다.

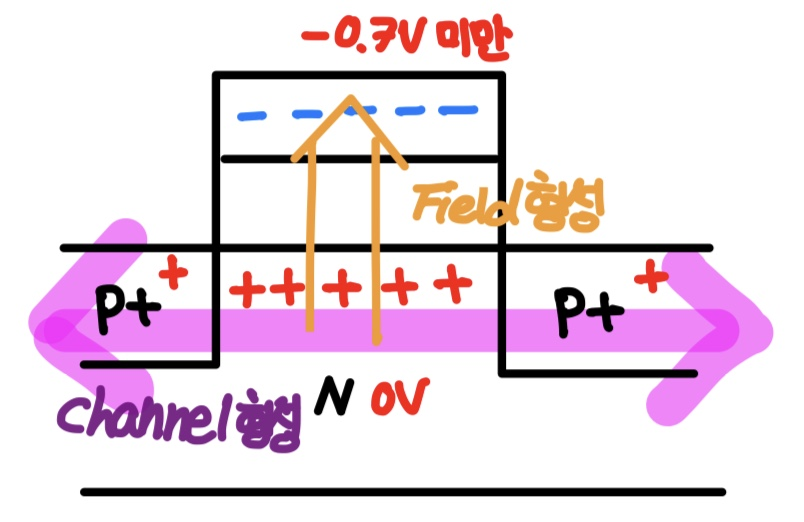

n-channel MOSFET

위 MOSFET을 예시로 들어보자.

여기서 전계는 Field를 의미하고 Source-Drain / Gate-Body 각각 사이에

전압을 걸어주면, 전위차에 의해 전계가 형성되고

문턱전압(Vt)을 넘게 되어 전기가 흐를 수 있는 형태가 된다.

이때문에 전계효과를 사용한다는 말을 쓰는 것이고, 낮은 전압을 Gate에 걸어줘도 도체로 변하여

Source-Drain 사이에 전압이 흐를 수 있기 때문에 전압 증폭 효과를 가진다

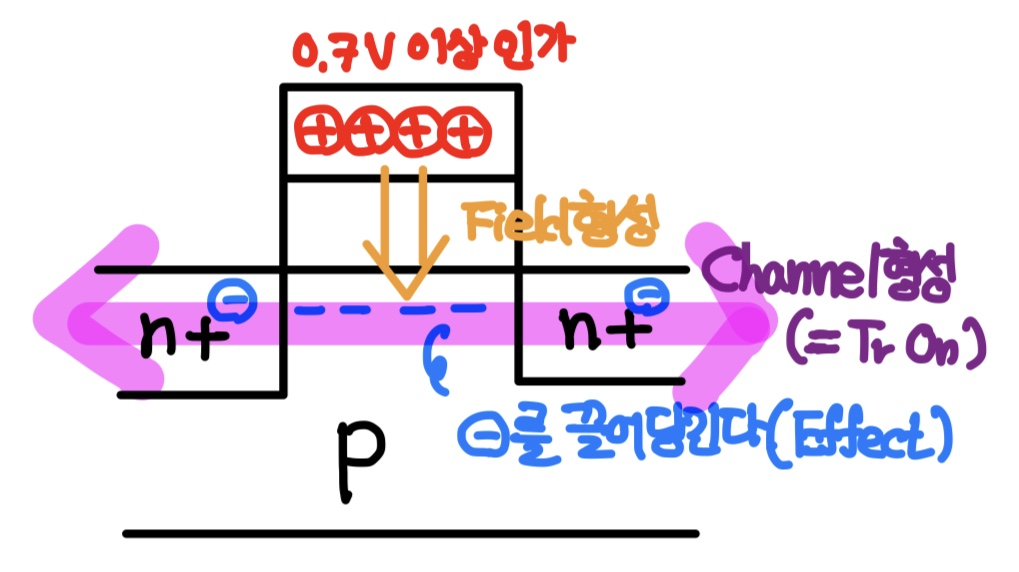

좀 더 자세히 설명하자면,

Gate에 문턱전압인 0.7V 이상의 전압을 인가하면, Field가 만들어지면서

P형 반도체에 있는 전자들을 끌어오고(Effect), 여기에 N형 반도체의 자유전자로 인해

채널이 형성된다. 이 채널을 통해 전류가 흐르게 되며, 이때를 Tr On 상태라고 부른다.

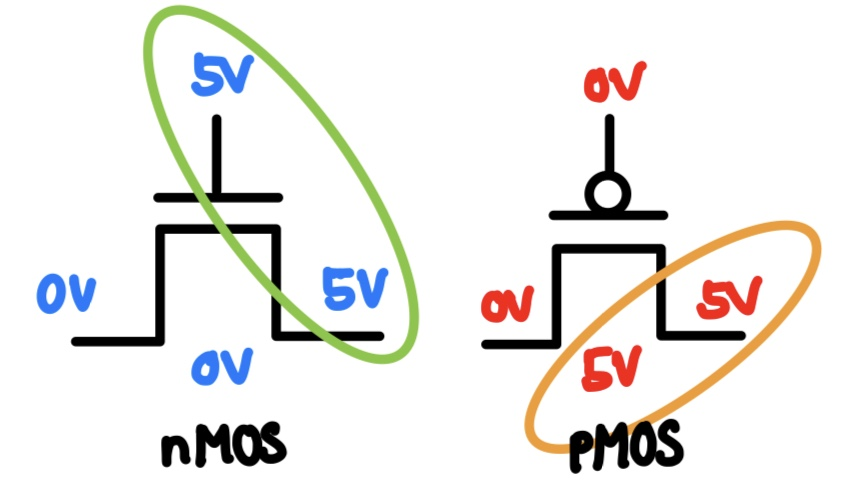

반대로 pMOS는 Gate측에 -전압을 걸어주면, 정공들이 가운데로 배치되면서 채널이 형성된다.

이로 인해 전기가 흐를 수 있는 상태가 되고 이 때를 Tr On 상태라고 한다.

위 심볼은 nMOS와 pMOS를 쉽게 표현한 그림이며, Source와 Drain의 위치는 바뀔 수 있다.

'# Semiconductor > - 반도체 이론' 카테고리의 다른 글

| 반도체의 기본 of 기본, MOSFET이란? (0) | 2023.07.14 |

|---|---|

| 반도체의 원리 - P/N형 반도체 PN접합, (0) | 2023.07.04 |

| 반도체란? - 반도체의 정의 및 특징, 소자, 반도체 종류 (0) | 2023.07.03 |